## STM32F072x8/xB Errata sheet

## STM32F072x8/xB device limitations

## Silicon identification

This document applies to the part numbers of STM32F072x8/xB devices listed in *Table 1* and their silicon revisions shown in *Table 2*.

Section 1 gives a summary and Section 2 a description of device limitations, with respect to the device datasheet and reference manual RM0091.

| Reference   | Part numbers                          |

|-------------|---------------------------------------|

| STM32F072x8 | STM32F072C8, STM32F072R8, STM32F072V8 |

| STM32F072xB | STM32F072CB, STM32F072RB, STM32F072VB |

#### Table 1. Device summary

## Table 2. Device identification<sup>(1)</sup>

| Reference      | Revision code marked on the device <sup>(2)</sup> |

|----------------|---------------------------------------------------|

| STM32F072x8/xB | 'Z', 'B', 'Y', '1'                                |

1. The REV\_ID bits in the DBGMCU\_IDCODE register indicate the revision code of the device (see the reference manual for details on the revision code).

2. Refer to datasheet for details on how to identify the silicon revision code on different types of package.

## Contents

| 1 | Sum  | mary of    | device limitations4                                                                                 |

|---|------|------------|-----------------------------------------------------------------------------------------------------|

| 2 | Desc | cription o | of device limitations6                                                                              |

|   | 2.1  | System     |                                                                                                     |

|   |      | 2.1.1      | Wakeup sequence from Standby mode when using more than one wakeup source                            |

|   |      | 2.1.2      | Over-consumption with regulator in Low power mode                                                   |

|   |      | 2.1.3      | ESD performance lower than expected6                                                                |

|   | 2.2  | USART      |                                                                                                     |

|   |      | 2.2.1      | Start bit detected too soon when sampling for NACK signal from the smartcard                        |

|   |      | 2.2.2      | Break request can prevent the Transmission Complete flag (TC) from being set                        |

|   |      | 2.2.3      | nRTS is active while RE or UE = 07                                                                  |

|   |      | 2.2.4      | Receiver timeout counter starting in case of 2 stops bit configuration 8                            |

|   |      | 2.2.5      | USART4 transmission does not work on PC118                                                          |

|   |      | 2.2.6      | Last byte written in TDR might not be transmitted if TE is cleared just after writing in TDR8       |

|   | 2.3  | GPIO .     |                                                                                                     |

|   |      | 2.3.1      | Input filter used when AF selected on PB9, PB10, PB148                                              |

|   |      | 2.3.2      | GPIOx locking mechanism not working properly for GPIOx_OTYPER register                              |

|   | 2.4  | I2C        | 9                                                                                                   |

|   |      | 2.4.1      | Wrong data sampling when data set-up time (t <sub>SU;DAT</sub> ) is shorter than one I2CCLK period9 |

|   |      | 2.4.2      | Spurious bus error detection in master mode9                                                        |

|   |      | 2.4.3      | 10-bit slave mode: wrong direction bit value after Read header reception                            |

|   |      | 2.4.4      | 10-bit combined with 7-bit slave mode: ADDCODE may indicate wrong slave address detection           |

|   |      | 2.4.5      | Wakeup frames may not wakeup the MCU mode when STOP mode entry follows I <sup>2</sup> C enabling    |

|   |      | 2.4.6      | Wakeup frame may not wakeup from STOP if t <sub>HD;STA</sub> is close to HSI startup time           |

|   |      | 2.4.7      | Wrong behavior in Stop mode when wakeup from Stop mode is disabled in $I^2C$                        |

|       | 2.4.8     | 10-bit master mode: new transfer cannot be launched if first part of the address has not been acknowledged by the slave |

|-------|-----------|-------------------------------------------------------------------------------------------------------------------------|

| 2.5   | SPI       |                                                                                                                         |

| 2.5   | -         |                                                                                                                         |

|       | 2.5.1     | BSY bit may stay high when SPI is disabled                                                                              |

|       | 2.5.2     | BSY bit may stay high at the end of a data transfer in slave mode 13                                                    |

|       | 2.5.3     | Wrong CRC transmitted in master mode with delayed SCK feedback . 14                                                     |

|       | 2.5.4     | CRC error in SPI slave mode if internal NSS changes before CRC transfer                                                 |

|       | 2.5.5     | SPI CRC corrupted upon DMA transaction completion by another peripheral                                                 |

|       | 2.5.6     | In I <sup>2</sup> S slave mode: WS level must be set by the external master when enabling the I2S                       |

| 2.6   | USB .     |                                                                                                                         |

|       | 2.6.1     | The USB BCD electrical parameter not in line with specification 16                                                      |

|       | 2.6.2     | The USB BCD functionality limited below -20°C                                                                           |

|       | 2.6.3     | DCD (data contact detect) function not compliant                                                                        |

| 2.7   | RTC .     |                                                                                                                         |

|       | 2.7.1     | Spurious tamper detection when disabling the tamper channel 16                                                          |

|       | 2.7.2     | A tamper event preceding the tamper detect enable not detected 17                                                       |

|       | 2.7.3     | RTC calendar registers are not locked properly                                                                          |

| 2.8   | ADC .     |                                                                                                                         |

|       | 2.8.1     | Overrun flag not set if EOC reset coincides with new conversion end . 17                                                |

|       | 2.8.2     | ADEN bit cannot be set immediately after the ADC calibration                                                            |

| 2.9   | COMP      |                                                                                                                         |

|       | 2.9.1     | Long V <sub>REFINT</sub> scaler startup time after power on                                                             |

| 2.10  | CEC .     |                                                                                                                         |

|       | 2.10.1    | Transmission blocked when transmitted start bit is corrupted                                                            |

| 2.11  | TSC .     |                                                                                                                         |

|       | 2.11.1    | Inhibited acquisition in short transfer phase configuration                                                             |

| 2.12  | bxCAN     |                                                                                                                         |

|       | 2.12.1    | bxCAN time-triggered communication mode not supported                                                                   |

| 2.13  |           |                                                                                                                         |

| 2.10  | 2.13.1    | RVU, PVU and WVU flags are not reset in STOP mode                                                                       |

|       | 2.13.2    | RVU, PVU and WVU flags are not reset with low-frequency APB 20                                                          |

|       |           | _,                                                                                                                      |

| Revis | sion hist | tory                                                                                                                    |

3

#### Summary of device limitations 1

The following table gives a quick references to all documented device limitations of STM32F072x8/xB and their status:

A = workaround available

- N = no workaround available

- P = partial workaround available

- "-" grayed = limitation not existing / limitation fixed

|          |         |                                                                                              |             | Status      |                  |

|----------|---------|----------------------------------------------------------------------------------------------|-------------|-------------|------------------|

| Function | Section | Limitation                                                                                   | Rev.<br>'Z' | Rev.<br>'B' | Rev.<br>'Y', '1' |

|          | 2.1.1   | Wakeup sequence from Standby mode when using more than one wakeup source                     | А           | А           | А                |

| System   | 2.1.2   | Over-consumption with regulator in Low power mode                                            | Ν           | -           | -                |

|          | 2.1.3   | ESD performance lower than expected                                                          | Ν           | -           | -                |

|          | 2.2.1   | Start bit detected too soon when sampling for NACK signal from the smartcard                 | Ν           | N           | N                |

|          | 2.2.2   | Break request can prevent the Transmission Complete flag (TC) from being set                 | А           | А           | А                |

| USART    | 2.2.3   | nRTS is active while RE or UE = 0                                                            | А           | Α           | Α                |

| USART    | 2.2.4   | Receiver timeout counter starting in case of 2 stops bit configuration                       | А           | А           | A                |

|          | 2.2.5   | USART4 transmission does not work on PC11                                                    | А           | Α           | Α                |

|          | 2.2.6   | Last byte written in TDR might not be transmitted if TE is cleared just after writing in TDR | A           | A           | A                |

|          | 2.3.1   | Input filter used when AF selected on PB9, PB10, PB14                                        | Р           | Р           | -                |

| GPIO     | 2.3.2   | GPIOx locking mechanism not working properly for GPIOx_OTYPER register                       | Ρ           | Р           | Р                |

|          | 2.4.1   | Wrong data sampling when data set-up time (tSU;DAT) is shorter than one I2CCLK period        | Ρ           | Р           | Р                |

|          | 2.4.2   | Spurious bus error detection in master mode                                                  | А           | Α           | Α                |

| 12C      | 2.4.3   | 10-bit slave mode: wrong direction bit value after Read header reception                     | А           | А           | А                |

|          | 2.4.4   | 10-bit combined with 7-bit slave mode: ADDCODE may indicate wrong slave address detection    | Ν           | N           | N                |

|          | 2.4.5   | Wakeup frames may not wakeup the MCU mode when STOP mode entry follows I2C enabling          | A           | A           | A                |

### Table 3. Summary of device limitations

|          |         |                                                                                                                            |             | Status      |                  |

|----------|---------|----------------------------------------------------------------------------------------------------------------------------|-------------|-------------|------------------|

| Function | Section | Limitation                                                                                                                 | Rev.<br>'Z' | Rev.<br>'B' | Rev.<br>'Y', '1' |

|          | 2.4.6   | Wakeup frame may not wakeup from STOP if tHD;STA is close to HSI startup time                                              | Ρ           | Р           | Р                |

| 12C      | 2.4.7   | Wrong behavior in Stop mode when wakeup from Stop mode is disabled in I2C                                                  | A           | A           | A                |

|          | 2.4.8   | 10-bit master mode: new transfer cannot be launched if first part<br>of the address has not been acknowledged by the slave | A           | A           | A                |

|          | 2.5.1   | BSY bit may stay high when SPI is disabled                                                                                 | А           | А           | А                |

|          | 2.5.2   | BSY bit may stay high at the end of a data transfer in slave mode                                                          | A           | A           | A                |

|          | 2.5.3   | Wrong CRC transmitted in master mode with delayed SCK feedback                                                             | A           | A           | A                |

| SPI      | 2.5.4   | CRC error in SPI slave mode if internal NSS changes before CRC transfer                                                    | А           | А           | A                |

|          | 2.5.5   | SPI CRC corrupted upon DMA transaction completion by another peripheral                                                    | Р           | Р           | Р                |

|          | 2.5.6   | In I2S slave mode: WS level must be set by the external master when enabling the I2S                                       | Α           | А           | Α                |

|          | 2.6.1   | The USB BCD electrical parameter not in line with specification                                                            | Ν           | -           | -                |

| USB      | 2.6.2   | The USB BCD functionality limited below -20°C                                                                              | Ν           | Ν           | Ν                |

|          | 2.6.3   | DCD (data contact detect) function not compliant                                                                           | Ν           | Ν           | Ν                |

|          | 2.7.1   | Spurious tamper detection when disabling the tamper channel                                                                | Р           | Р           | Р                |

| RTC      | 2.7.2   | A tamper event preceding the tamper detect enable not detected                                                             | А           | A           | A                |

|          | 2.7.3   | RTC calendar registers are not locked properly                                                                             | Α           | А           | А                |

| ADC      | 2.8.1   | Overrun flag not set if EOC reset coincides with new conversion end                                                        | A           | A           | A                |

|          | 2.8.2   | ADEN bit cannot be set immediately after the ADC calibration                                                               | Α           | А           | А                |

| COMP     | 2.9.1   | Long VREFINT scaler startup time after power on                                                                            | Ν           | N           | N                |

| CEC      | 2.10.1  | Transmission blocked when transmitted start bit is corrupted                                                               | Р           | Р           | Р                |

| TSC      | 2.11.1  | Inhibited acquisition in short transfer phase configuration                                                                | Р           | Р           | Р                |

| bxCAN    | 2.12.1  | bxCAN time-triggered communication mode not supported                                                                      | Ν           | Ν           | Ν                |

| IWDG     | 2.13.1  | RVU, PVU and WVU flags are not reset in STOP mode                                                                          | А           | А           | Α                |

| IVVDG    | 2.13.2  | RVU, PVU and WVU flags are not reset with low-frequency APB                                                                | Ν           | N           | Ν                |

Table 3. Summary of device limitations (continued)

## 2 Description of device limitations

The following sections describe device limitations and provide workarounds if available. They are grouped by device functions.

## 2.1 System

## 2.1.1 Wakeup sequence from Standby mode when using more than one wakeup source

## Description

The various wakeup sources are logically OR-ed in front of the rising-edge detector which generates the wakeup flag (WUF). The WUF needs to be cleared prior to Standby mode entry, otherwise the MCU wakes up immediately.

If one of the configured wakeup sources is kept high during the clearing of the WUF (by setting the CWUF bit), it may mask further wakeup events on the input of the edge detector. As a consequence, the MCU might not be able to wake up from Standby mode.

## Workaround

To avoid this problem, the following sequence should be applied before entering Standby mode:

- Disable all used wakeup sources,

- Clear all related wakeup flags,

- Re-enable all used wakeup sources,

- Enter Standby mode

- Note: Be aware that, when applying this workaround, if one of the wakeup sources is still kept high, the MCU will enter Standby mode but then it wakes up immediately generating a power reset.

## 2.1.2 Over-consumption with regulator in Low power mode

### Description

Current consumption in Stop mode could be higher by approximately 15 uA for LP regulator mode than for run mode under same conditions. This is seen mainly at temperature above  $85^{\circ}$ C and with VDD > 3.2V.

### Workaround

None.

## 2.1.3 ESD performance lower than expected

### Description

Device shows lower ESD performance than the other products from STM32F0 family.

## Workaround

None.

## 2.2 USART

## 2.2.1 Start bit detected too soon when sampling for NACK signal from the smartcard

## Description

In the ISO7816, when a character parity error is incorrect, the smartcard receiver shall transmit a NACK error signal at (10.5 + - 0.2) etu after the character START bit falling edge. In this case, the USART transmitter should be able to detect correctly the NACK signal by sampling at (11.0 + -0.2) etu after the character START bit falling edge.

The USART peripheral used in smartcard mode doesn't respect the (11 +/-0.2) etu timing, and when the NACK falling edge arrives at 10.68 etu or later, the USART might misinterpret this transition as a START bit even if the NACK is correctly detected.

## Workaround

None

## 2.2.2 Break request can prevent the Transmission Complete flag (TC) from being set

## Description

After the end of transmission of a data (D1), the Transmission Complete (TC) flag will not be set in the following conditions:

- CTS hardware flow control is enabled.

- D1 is being transmitted.

- A break transfer is requested before the end of D1 transfer.

- nCTS is de-asserted before the end of transfer of D1.

## Workaround

If the application needs to detect the end of transfer of the data, the break request should be done after making sure that the TC flag is set.

## 2.2.3 nRTS is active while RE or UE = 0

### Description

The nRTS line is driven low as soon as RTSE bit is set even if the USART is disabled (UE = 0 or the receiver is disabled (RE = 0) i.e. not ready to receive data.

### Workaround

Configure the I/O used for nRTS as alternate function after setting the UE and RE bits.

DocID025328 Rev 4

## 2.2.4 Receiver timeout counter starting in case of 2 stops bit configuration

## Description

In the case of 2 stop bits configuration, the receiver timeout counter starts counting from the end of the second stop bit of the last character instead of the end of the first stop bit.

## Workaround

Change the RTO value in the USARTx\_RTOR register by subtracting 1 bit duration.

## 2.2.5 USART4 transmission does not work on PC11

## Description

USART4\_RX does not work as output on PC11.

As a consequence, single wire half duplex mode is not supported with pin PC11.

## Workaround

Use USART4\_RX mapped on PA0 instead on PC11.

## 2.2.6 Last byte written in TDR might not be transmitted if TE is cleared just after writing in TDR

## Description

If the USART clock source is slow (for example LSE) and TE bit is cleared immediately after the last write to TDR, the last byte will probably not be transmitted.

## Workarounds

- 1. Wait until TXE flag is set before clearing TE bit

- 2. Wait until TC flag is set before clearing TE bit

## 2.3 GPIO

## 2.3.1 Input filter used when AF selected on PB9, PB10, PB14

### Description

When the AF5 (SPI2/I2S2) is chosen on PB9, PB10, or the AF1 (TIM15\_CH1) is chosen on PB14, input signal is routed through  $I^2C$  input filters instead or direct connection and signal is impacted by the  $I^2C$  filters.

## Workaround

Deactivate analog filters on  $I^2C$  pads (I2C1 for PB9, I2C2 for PB10 and PB14) with software. However, the  $I^2C$  cannot use the filters at the same time on any other pads.

## 2.3.2 GPIOx locking mechanism not working properly for GPIOx\_OTYPER register

### Description

Locking of GPIOx\_OTYPER[i] with i = 15..8 depends from setting of GPIOx\_LCKR[i-8] and not from GPIOx\_LCKR[i]. GPIOx\_LCKR[i-8] is locking GPIOx\_OTYPER[i] together with GPIOx\_OTYPER[i-8]. It is not possible to lock GPIOx\_OTYPER[i] with i = 15...8, without locking also GPIOx\_OTYPER[i-8].

### Workaround

The only way to lock GPIOx\_OTYPER[i] with i=15..8 is to lock also GPIOx\_OTYPER[i-8].

## 2.4 I2C

## 2.4.1 Wrong data sampling when data set-up time (t<sub>SU;DAT</sub>) is shorter than one I2CCLK period

### Description

The I<sup>2</sup>C-bus specification and user manual specify a minimum data set-up time (t<sub>SU:DAT</sub>) as:

- 250 ns in Standard mode

- 100 ns in Fast mode

- 50 ns in Fast mode Plus

The I<sup>2</sup>C-bus SDA line is not correctly sampled when  $t_{SU;DAT}$  is smaller than one I2CCLK (I<sup>2</sup>C-bus peripheral clock) period: the previous SDA value is sampled instead of the current one. This can result in a wrong receipt of slave address, data byte, or acknowledge bit.

### Workaround

Increase the I2CCLK frequency to get I2CCLK period within the transmitter minimum data set-up time. Alternatively, increase transmitter's minimum data set-up time.

## 2.4.2 Spurious bus error detection in master mode

### Description

In master mode, a bus error can be detected by mistake, so the BERR flag can be wrongly raised in the status register. This will generate a spurious Bus Error interrupt if the interrupt is enabled. A bus error detection has no effect on the transfer in master mode, therefore the I2C transfer can continue normally.

### Workaround

If a bus error interrupt is generated in master mode, the BERR flag must be cleared by software. No other action is required and the on-going transfer can be handled normally.

## 2.4.3 10-bit slave mode: wrong direction bit value after Read header reception

## Description

Under specific conditions, the transfer direction bit DIR (bit 16 of status register I2C\_ISR) is low instead of high after reception of the 10-bit addressing Read header. Nevertheless, the I<sup>2</sup>C operates correctly in slave transmission mode, and data can be sent using the TXIS flag.

To see the limitation, all the following conditions have to be fulfilled:

- I<sup>2</sup>C has to be configured in 10-bit addressing mode (OA1MODE is set in the I2C\_OAR1 register).

- The high LSBs of the I<sup>2</sup>C slave address are equal to the 10-bit addressing Read header value (i.e. OA1[7:3] = 11110, OA1[2] = OA1[9], OA1[1] = OA1[8] and OA1[0] = 1 in the I2C\_OAR1 register).

- The I<sup>2</sup>C receives the 10-bit addressing Read header (0X 1111 0XX1) after the repeated start condition to enter slave transmission mode.

As a result, the DIR bit is incorrect in slave mode under specific conditions.

## Workaround

If possible, do not use these four values as 10-bit addresses in slave mode:

- OA1[9:0] = 0011110001

- OA1[9:0] = 0111110011

- OA1[9:0] = 1011110101

- OA1[9:0] = 1111110111

If one of these addresses is the  $I^2C$  slave address, the DIR bit must not be used in the FW.

## 2.4.4 10-bit combined with 7-bit slave mode: ADDCODE may indicate wrong slave address detection

## Description

Under specific conditions, the ADDCODE (Address match code) in the I2C\_ISR register indicates a wrong slave address.

To see the limitation, all the following conditions have to be fulfilled:

- The I<sup>2</sup>C slave address OA1 is enabled and configured in 10-bit mode (OA1EN=1 and OA1MODE=1)

- Another 7-bit slave address is enabled and the bits 1 to 7 of the 10-bit slave address OA1 are equal to the 7-bit slave address, i.e., one of the configurations below is set:

- OA2EN=1 and OA2MSK = 0 and OA1[7:1] = OA2[7:1]

- OA2EN=1 and OA2MSK = 1 and OA1[7:2] = OA2[7:2]

- OA2EN=1 and OA2MSK = 2 and OA1[7:3] = OA2[7:3]

- OA2EN=1 and OA2MSK = 3 and OA1[7:4] = OA2[7:4]

- OA2EN=1 and OA2MSK = 4 and OA1[7:5] = OA2[7:5]

- OA2EN=1 and OA2MSK = 5 and OA1[7:6] = OA2[7:6]

- OA2EN=1 and OA2MSK = 6 and OA1[7] = OA2[7]

- OA2EN=1 and OA2MSK = 7

- GCEN=1 and OA1[7:1] = 0b0000000

- ALERTEN=1 and OA1[7:1] = 0b0001100

- SMBDEN=1 and OA1[7:1] = 0b1100001

- SMBHEN=1 and OA1[7:1] = 0b0001000

- The master starts a transfer addressed to the 10-bit slave address OA1.

As a result, after the address reception, the ADDCODE value is OA1[7:1] equal to the 7-bit slave address, instead of 0b11110 & OA1[9:8].

### Workaround

None. If several slave addresses are enabled, mixing 10-bit and 7-bit addresses, the 10-bit Slave address OA1 [7:1] must not be equal to the 7-bit slave address.

# 2.4.5 Wakeup frames may not wakeup the MCU mode when STOP mode entry follows I<sup>2</sup>C enabling

### Description

If the  $I^2C$  is enabled (PE = 1) and wakeup from STOP enabled in  $I^2C$  (WUPEN=1) while a transfer occurs on the  $I^2C$  bus and STOP mode is entered during the same transfer while SCL=0, the  $I^2C$  is not able to detect the following START condition. This means that if the  $I^2C$  is addressed, it will not wake up the MCU and this address is not acknowledged.

#### Workaround

After enabling the  $I^2C$  (PE is set to 1), wait for a temporization before entering STOP mode, to ensure that the eventual on-going frame is finished.

# 2.4.6 Wakeup frame may not wakeup from STOP if t<sub>HD;STA</sub> is close to HSI startup time

### Description

Under specific conditions and if the START condition hold time  $t_{HD;STA}$  duration is very close to the HSI start-up time duration, the I<sup>2</sup>C is not able to detect the address match and wake up the MCU from STOP.

To see the limitation, one of the conditions listed below has to be met:

- 1. Timeout detection is enabled (TIMOUTEN=1 or TEXTEN=1) and the frame before the wakeup frame is abnormally finished due to a I<sup>2</sup>C Timeout detection (TIMOUT=1).

- 2. The slave arbitration is lost during the frame before the wakeup frame (ARLO=1).

- 3. The MCU enters STOP mode while another slave is addressed, after the address phase and before the STOP condition (BUSY=1).

- 4. The MCU is in STOP mode and another slave is addressed before the I<sup>2</sup>C is addressed.

- Note: The last conditions 2, 3 and 4 can occur only in a multi-slave network.

In STOP mode, the HSI is switched on by the I<sup>2</sup>C when a START condition is detected (SDA falling edge while SCL is high). The HSI is used to receive the address. HSI is switched off after the address reception if received address is not the I<sup>2</sup>C slave address. If one of the

DocID025328 Rev 4

conditions above is met and if the SCL falling edge following the START condition occurs on the first cycle of the I2CCLK clock (HSI), the address reception is not correctly done and the address match wakeup interrupt is not generated.

## Workaround

None at MCU level.

If the wakeup frame is not acknowledged by the I<sup>2</sup>C and if the master can program the duration of the START hold time: the master should decrease or increase the START condition hold time for more than one HSI period and resend the wakeup frame.

# 2.4.7 Wrong behavior in Stop mode when wakeup from Stop mode is disabled in I<sup>2</sup>C

## Description

When wakeup from Stop mode is disabled in  $I^2C$  (WUPEN = 0) and the MCU enters Stop mode while a transfer is on going on the bus, some wrong behaviors may happen:

- 1. BUSY flag can be wrongly set when the MCU exits Stop mode. This prevents from initiating a transfer in master mode, as the START condition cannot be sent when BUSY is set.

- 2. If clock stretching is enabled (NOSTRETCH = 0), the  $l^2C$  clock SCL may be stretched low by the  $l^2C$  as long as the MCU is in Stop mode. This limitation may occur when the Stop mode is entered during the address phase of a transfer on the  $l^2C$  bus while SCL = 0. Therefore the transfer may be stalled as long as the MCU is in Stop mode. The probability of the occurrence depends also on the timings configuration, the peripheral clock frequency and the  $l^2C$  bus frequency.

These behaviors can occur in Slave mode and in Master mode in a multi-master topology.

### Workaround

Disable the I<sup>2</sup>C (PE=0) before entering Stop mode and re-enable it in Run mode.

## 2.4.8 10-bit master mode: new transfer cannot be launched if first part of the address has not been acknowledged by the slave

## Description

In master mode, the master automatically sends a STOP bit when the slave has not acknowledged a byte during the address transmission.

In 10-bit addressing mode, if the first byte of the 10-bit address (5-bit header + 2 MSBs of the address + direction bit) has not been acknowledged by the slave, the STOP bit is sent but the START bit is not cleared and the master cannot launch a new transfer.

## Workaround

When the I2C is configured in 10-bit addressing master mode and the NACKF status flag is set in the I2C\_ISR register while the START bit is still set in I2C\_CR2 register, then proceed as follows:

- 1. Wait for the STOP condition detection (STOPF = 1 in I2C\_ISR register).

- 2. Disable the I2C peripheral.

- 3. Wait for a minimum of 3 APB cycles.

- 4. Enable the I2C peripheral again.

## 2.5 SPI

## 2.5.1 BSY bit may stay high when SPI is disabled

### Description

The BSY flag may remain high upon disabling the SPI while operating in:

- a master transmit mode and the TXE flag is low (data register full).

- a master receive only mode (simplex receive or half-duplex bidirectional receive phase) and an SCK strobing edge has not occurred since the transition of the RXNE flag from low to high.

- slave mode and NSS signal is removed during the communication.

## Workaround

When the SPI operates in:

- a master transmit mode, disable the SPI when TXE=1 and BSY=0.

- a master receive only mode, ignore the BSY flag.

- slave mode, do not remove the NSS signal during the communication.

## 2.5.2 BSY bit may stay high at the end of a data transfer in slave mode

### Description

In slave mode, The BSY bit is not reliable to handle the end of data frame transaction due to some bad synchronization between the CPU clock and external SCK clock provided by the SPI master. Sporadically, the BSY bit is not cleared at the end of a data frame transfer. As a consequence, it is not recommended to rely on the BSY bit before entering low-power mode or modifying the SPI configuration (e.g. direction of the bidirectional mode).

## Workaround

- When the SPI interface is in receive mode, the end of a transaction with the master can be detected by the corresponding RXNE event when this flag is set after the last bit of that transaction is sampled and the received data are stored.

- When the following sequence is used, the synchronization issue does not occur. The BSY bit works correctly and can be used to recognize the end of any transmission transaction (including when RXNE is not raised in bidirectional mode):

- a) Write the last data into data register.

- b) Poll the TXE flag till it becomes high to make sure the data transfer has started.

- c) Disable the SPI interface by clearing the SPE bit while the last data transfer is on going.

- d) Poll the BSY bit till it becomes low.

Note: The second workaround can be used only when the CPU is fast enough to disable the SPI interface after a TXE event is detected while the data frame transfer is ongoing. It cannot be implemented when the ratio between CPU and SPI clock is low and the data frame is particularly short. At this specific case, the timeout can be measured from the TXE event instead by calculating a fixed number of CPU clock cycles corresponding to the time necessary to complete the data frame transaction.

## 2.5.3 Wrong CRC transmitted in master mode with delayed SCK feedback

## Description

In transmit transaction of the SPI/I<sup>2</sup>S interface in SPI master mode with CRC enabled, the CRC data transmission may be corrupted if the delay of an internal feedback signal derived from the SCK output (further feedback clock) is greater than one APB clock period. While data and CRC bit shifting and transfer is based on an internal clock, the CRC progressive calculation uses the feedback clock. If the delay of the feedback clock is greater than one APB period, the transmitted CRC value may get wrong.

The main factors contributing to the delay increase are low  $V_{DD}$  level, high temperature, high SCK pin capacitive load and low SCK IO output speed. The SPI communication speed has no impact.

## Workaround

Set the application such as to speed up the SCK edges and / or slow down the APB clock, through:

- configuring the SCK output GPIO so as to reach lower output impedance

- minimizing the capacitive load on the SCK output line

- configuring the APB clock speed

## 2.5.4 CRC error in SPI slave mode if internal NSS changes before CRC transfer

## Description

When the device is configured as SPI slave, the transition of the internal NSS after the CRCNEXT flag is set may result in wrong CRC value computed by the device and, as a

consequence, a CRC error. As a consequence, the NSS pulse mode cannot be used along with the CRC function.

## Workaround

Prevent the internal NSS signal from changing in the critical period, by configuring the device to software NSS control if the SPI master pulses the NSS (for example in NSS pulse mode).

## 2.5.5 SPI CRC corrupted upon DMA transaction completion by another peripheral

#### Description

When the following conditions are all met:

- CRC function for the SPI is enabled,

- SPI transaction managed by software (as opposed to DMA) is ongoing and CRCNEXT flag set,

- another peripheral using the same DMA channel on which the SPI is mapped completes a DMA transfer,

the CRCNEXT bit is unexpectedly cleared and the SPI CRC calculation may be corrupted, setting the CRC error flag.

#### Workaround

If possible, do not use the DMA channel, on which the SPI is mapped, by any other peripheral.

If possible, remap SPI2 to a DMA channel not used by another peripheral.

## 2.5.6 In I<sup>2</sup>S slave mode: WS level must be set by the external master when enabling the I2S

#### Description

In slave mode, the WS signal level is used only to start the communication. If the I2S (in slave mode) is enabled while the master is already sending the clock and the WS signal level is low (for I<sup>2</sup>S protocol) or is high (for the LSB or MSB-justified mode), the slave starts communicating data immediately. In this case, the master and slave will be desynchronized throughout the whole communication.

### Workaround

The I2S peripheral must be enabled when the external master sets the WS line at:

- High level when the I<sup>2</sup>S protocol is selected.

- Low level when the LSB or MSB-justified mode is selected.

## 2.6 USB

## 2.6.1 The USB BCD electrical parameter not in line with specification

## Description

USB BCD in Primary and Secondary detection mode can have under some conditions the regulated voltage threshold level smaller than the minimum specified.

This parameter deviation is a limitation to use the BCD, but only when connected to a CDP port in one specific configuration.

## Workaround

None.

This limitation is present on Revision Z only.

## 2.6.2 The USB BCD functionality limited below -20°C

## Description

Primary and secondary detection can return an incorrectly detected port type.

This limitation may be observed on a small number of devices when the temperature is below -20°C.

## Workaround

None.

## 2.6.3 DCD (data contact detect) function not compliant

### Description

The DCD function on the device is not compliant with the "USB Battery Charging 1.2 Compliance Plan rev 1.0" specification.

### Workaround

Do not use the DCD function. Instead, upon attaching a USB device, wait for at least "TDCD\_TIMEOUT" amount of time before starting Primary Detection. This is in line with the "Battery Charging Specification rev1.2" recommendation for portable devices that do not support the DCD function.

## 2.7 RTC

## 2.7.1 Spurious tamper detection when disabling the tamper channel

## Description

If the tamper detection is configured for detecting on falling-edge event (TAMPFLT[1:0]=00 and TAMPxTRG=1) and if the tamper event detection is disabled when the tamper pin is at

high level, a false detection of a tamper event occurs, which may result in the erasure of backup registers.

#### Workaround

The false detection of tamper event cannot be avoided. The erasure of the backup registerscan be avoided by setting the TAMPxNOERASE bit before clearing the TAMPxE bit, in two separate RTC\_TAMPCR write accesses.

## 2.7.2 A tamper event preceding the tamper detect enable not detected

#### Description

When the tamper detect is enabled, set in edge detection mode (TAMPFLT[1:0]=00), and

- set to active rising edge (TAMPxTRG=0): if the tamper input is already high (tamper event already occurred) at the moment of enabling the tamper detection, the tamper event may not be detected. The probability of detection increases with the APB frequency.

- set to active falling edge (TAMPxTRG=1): if the tamper input is already low (tamper event already occurred) at the moment of enabling the tamper detection, the tamper event is not detected.

#### Workaround

The I/O state should be checked by software in the GPIO registers, after enabling the tamper detection and before writing sensitive values in the backup registers, in order to ensure that no active edge occurred before enabling the tamper event detection.

## 2.7.3 RTC calendar registers are not locked properly

### Description

When reading the calendar registers with BYPSHAD=0, the RTC\_TR and RTC\_DR registers may not be locked after the read of RTC\_SSR register. This happens if the read of RTC\_SSR is initiated one APB clock period before the shadow registers are updated. This can result in a non-consistency of the 3 registers. Similarly, RTC\_DR register can be updated after the read of the RTC\_TR register instead of being locked.

### Workaround

- 1. Use BYPSHAD = 1 mode (Bypass shadow registers), or

- 2. In case BYPSHAD = 0: read SSR again after reading SSR/TR/DR to confirm that SSR is still the same, otherwise read the values again.

## 2.8 ADC

## 2.8.1 Overrun flag not set if EOC reset coincides with new conversion end

### Description

If the EOC flag is cleared by ADC\_DR register read operation or by software during the same APB cycle in which the data from a new conversion are written in the ADC\_DR

DocID025328 Rev 4

register, the overrun event duly occurs (which results in the loss of either current or new data) but the overrun flag (OVR) may stay low.

## Workaround

Clear the EOC flag through ADC\_DR register read operation or by software within less than one ADC conversion cycle period from the last conversion cycle end, so as to avoid the coincidence with the new conversion cycle end.

## 2.8.2 ADEN bit cannot be set immediately after the ADC calibration

## Description

At the end of the ADC calibration, an internal reset of ADEN bit occurs four ADC clock cycles after the ADCAL bit is cleared by hardware. As a consequence, if the ADEN bit is set within those four ADC clock cycles, it is reset shortly after by the calibration logic and the ADC remains disabled.

## Workaround

- 1. Keep setting the ADEN bit until the ADRDY flag goes high.

- 2. After the ADCAL is cleared, wait for a minimum of four ADC clock cycles before setting the ADEN bit.

## 2.9 COMP

## 2.9.1 Long V<sub>REFINT</sub> scaler startup time after power on

### Description

The V<sub>REFINT</sub> scaler is an embedded voltage follower providing the V<sub>REFINT</sub> or its fractions (1/2, 1/4 or 3/4) to the comparator input.

The maximum  $V_{REFINT}$  scaler startup time  $t_{S\_SC}(max)$ , specified to 0.2 ms, is not respected for the first activation of the  $V_{REFINT}$  scaler after powering on the device. In worst-case conditions, it can be as much as 1 s. The startup time depends mainly on the voltage and temperature. See the device datasheet for more details.

### Workaround

None.

## 2.10 CEC

## 2.10.1 Transmission blocked when transmitted start bit is corrupted

## Description

When the HDMI-CEC communication start bit transmitted by the device is corrupted by another device on the CEC line, the CEC transmission is stalled.

This failure is unlikely to happen as the CEC start bit corruption by another device can only occur if that device does not respect the CEC communication protocol.

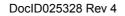

The start bit timing standard tolerances are shown in *Figure 1*. The start bit is initiated by the device by driving the CEC line low (reference point). After 3.7 ms, the device releases the CEC line and starts checking its level. The following conditions must be met for the start bit to be valid:

- the CEC line goes high no later than 3.9 ms (4.05 ms with extended tolerance) from the reference point

- a falling edge on the CEC line does not occur earlier than 4.3 ms (4.15 ms with extended tolerance) from the reference point

If one of these conditions is not met, the transmission is aborted and never automatically retried. No error flag is set and the TXSOM (Tx Start Of Message) bit is not cleared.

#### Figure 1. HDMI-CEC start bit format with tolerances

### Workaround

A way to work this limitation around is for the system-level CEC application software to start a time-out counter when setting TXSOM bit and stop it upon TXBR or TXEND event. In case of time-out, the HDMI-CEC functional block is disabled then enabled, by setting the CECEN bit in CEC\_CR register to 0 then to 1. This clears the TXSOM bit.

## 2.11 TSC

## 2.11.1 Inhibited acquisition in short transfer phase configuration

### Description

The GPIO input buffer is masked outside the transfer window time and then sampled twice before being checked for the acquisition. This check is performed on the last touch sensing clock cycle of the charge transfer phase. When the charge transfer duration is less than three clock cycles, the acquisition is inhibited.

### Workaround

Do not use the following TSC control register configurations:

- PGPSC[2:0] bits set to 000 and CTPL[3:0] bits set to 0000 or 0001 in TSC\_CR register

- PGPSC[2:0] bits set to 001 and bits CTPL[3:0] set to 0000 in TSC\_CR register

## 2.12 bxCAN

## 2.12.1 bxCAN time-triggered communication mode not supported

## Description

The time-triggered communication mode is not supported. As a consequence, timestamp values are not available. The TTCM bit in the CAN\_MCR register must be kept at 0 (time-triggered communication mode disabled).

## Workaround

None

## 2.13 IWDG

## 2.13.1 RVU, PVU and WVU flags are not reset in STOP mode

## Description

The RVU,PVU and WVU flags of the IWDG\_SR register are set by hardware after a write access to the IWDG\_RLR and the IWDG\_PR registers, respectively. If the Stop mode is entered immediately after the write access, the RVU,PVU and WVU flags are not reset by hardware. Before performing a second write operation to the IWDG\_RLR or the IWDG\_PR register, the application software must wait for the RVU, PVU and WVU flags to be reset. However, since the RVU/PVU/WPU bit is not reset after exiting the Stop mode, the software goes into an infinite loop and the independent watchdog (IWDG) generates a reset after the programmed timeout period.

## Workaround

Wait until the RVU, PVU and WVU flags of the IWDG\_SR register are reset, before entering the Stop mode.

## 2.13.2 RVU, PVU and WVU flags are not reset with low-frequency APB

## Description

The RVU, PVU and WVU flags of the IWDG\_SR register are set by hardware after a write access to the IWDG\_RLR and the IWDG\_PR registers, respectively. If the APB clock frequency is two times slower than the IWDG clock frequency, the RVU, PVU and WVU flags will never be reset by hardware.

## Workaround

None

## 3 Revision history

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12-Nov-2013 | 1        | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 13-Jan-2014 | 2        | Added silicon revision 'Y'<br>Added section: The USB BCD functionality limited below<br>-20°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 04-Apr-2014 | 3        | <ul> <li>Workaround in section: Extra consumption on GPIOs<br/>PC05 on 48/49 pin packages and summary table<br/>modified to indicate that the product does not have this<br/>limitation.</li> <li>Added section: USART4 transmission does not work on<br/>PC11</li> <li>Added section: Input filter used when AF selected on<br/>PB9, PB10, PB14</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 12-Oct-2016 | 4        | <ul> <li>Added:<br/>USART:</li> <li>Section 2.2.1: Start bit detected too soon when<br/>sampling for NACK signal from the smartcard</li> <li>Section 2.2.2: Break request can prevent the<br/>Transmission Complete flag (TC) from being set</li> <li>Section 2.2.3: nRTS is active while RE or UE = 0</li> <li>Section 2.2.4: Receiver timeout counter starting in<br/>case of 2 stops bit configuration</li> <li>I2C:</li> <li>Section 2.4.1: Wrong data sampling when data set-up<br/>time (tSU;DAT) is shorter than one I2CCLK period</li> <li>Section 2.4.2: Spurious bus error detection in master<br/>mode</li> <li>Section 2.4.8: 10-bit master mode: new transfer<br/>cannot be launched if first part of the address has not<br/>been acknowledged by the slave</li> <li>SPI:</li> <li>Section 2.5.1: BSY bit may stay high when SPI is<br/>disabled</li> <li>Section 2.5.3: Wrong CRC transmitted in master<br/>mode with delayed SCK feedback</li> <li>Section 2.5.4: CRC error in SPI slave mode if internal<br/>NSS changes before CRC transfer</li> <li>Section 2.5.5: SPI CRC corrupted upon DMA<br/>transaction completion by another peripheral<br/>USB:</li> <li>Section 2.6.3: DCD (data contact detect) function not<br/>compliant</li> </ul> |

| Date        | Revision | Changes                                                                                                                                                                                                                      |

|-------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             |          | RTC:                                                                                                                                                                                                                         |

|             |          | <ul> <li>Section 2.7.1: Spurious tamper detection when<br/>disabling the tamper channel</li> </ul>                                                                                                                           |

|             |          | <ul> <li>Section 2.7.2: A tamper event preceding the tamper<br/>detect enable not detected</li> </ul>                                                                                                                        |

|             |          | <ul> <li>Section 2.7.3: RTC calendar registers are not locked<br/>properly</li> </ul>                                                                                                                                        |

|             |          | ADC:                                                                                                                                                                                                                         |

|             |          | <ul> <li>Section 2.8.1: Overrun flag not set if EOC reset<br/>coincides with new conversion end</li> </ul>                                                                                                                   |

|             |          | <ul> <li>Section 2.8.2: ADEN bit cannot be set immediately<br/>after the ADC calibration</li> </ul>                                                                                                                          |

|             |          | COMP:                                                                                                                                                                                                                        |

|             |          | <ul> <li>Section 2.9.1: Long VREFINT scaler startup time after<br/>power on</li> </ul>                                                                                                                                       |

|             |          | CEC:                                                                                                                                                                                                                         |

|             |          | <ul> <li>Section 2.10.1: Transmission blocked when<br/>transmitted start bit is corrupted</li> </ul>                                                                                                                         |

|             |          | TSC:                                                                                                                                                                                                                         |

| 12-Oct-2016 | 4        | <ul> <li>Section 2.11.1: Inhibited acquisition in short transfer<br/>phase configuration</li> </ul>                                                                                                                          |

|             |          | bxCAN:                                                                                                                                                                                                                       |

|             |          | <ul> <li>Section 2.12.1: bxCAN time-triggered communication<br/>mode not supported</li> </ul>                                                                                                                                |

|             |          | IWDG:                                                                                                                                                                                                                        |

|             |          | <ul> <li>Section 2.13.1: RVU, PVU and WVU flags are not reset in STOP mode</li> </ul>                                                                                                                                        |

|             |          | <ul> <li>Section 2.13.2: RVU, PVU and WVU flags are not reset with low-frequency APB</li> </ul>                                                                                                                              |

|             |          | Modified:                                                                                                                                                                                                                    |

|             |          | <ul> <li>Document structure</li> </ul>                                                                                                                                                                                       |

|             |          | - Cover page and Table 3 organization                                                                                                                                                                                        |

|             |          | Removed:                                                                                                                                                                                                                     |

|             |          | <ul> <li>– GPIO: Extra consumption on GPIOs PC05 on 48/49<br/>pin packages (This limitation does not exist on the<br/>product. It was kept in the previous revisions of the<br/>document for historical reasons.)</li> </ul> |

|             |          | <ul> <li>Appendix A (package marking drawings are now<br/>available in the data sheet)</li> </ul>                                                                                                                            |

| Table 4. Document revision history (continued) |

|------------------------------------------------|

|------------------------------------------------|

#### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2016 STMicroelectronics – All rights reserved

DocID025328 Rev 4