Document Number: T4240PB Rev 1, 10/2014

# T4240 Product Brief Also supports T4160 and T4080

## **1** Introduction

The QorIQ T4 family of processors combine Freescale advanced, dual-threaded e6500 Power Architecture® processor cores with AltiVec, high-performance data path acceleration architecture (DPAA), and network and peripheral interfaces to address a wide variety of applications in networking, telecom/datacom, data center, wireless infrastructure, industrial and mil/aerospace applications.

The T4 family consists of three devices:

- The T4240 QorIQ multicore processor combines 12 dual-threaded e6500 Power Architecture processor cores for a total of 24 threads.

- The T4160 QorIQ multicore processor combines 8 dualthreaded e6500 Power Architecture processor cores. For more details on T4160 see Appendix T4160.

- The T4080 QorIQ multicore processor combines 4 dualthreaded e6500 Power Architecture processor cores. For more details on T4080 see Appendix T4080.

The T4 family has a 3x performance scaling factor within a pin-compatible package. With frequencies scaling from 1.5 to 1.8 GHz, integrated 1 Gbps and 10 Gbps Ethernet, hardware acceleration, and advanced system peripherals, these products target applications that benefit from consolidation of control and data plane processing in a single chip, such as services cards, microservers, NFV, SDN, ADCs, WOCs, and intelligent NICs.

#### Contents

| 1 | Introduction                 | 1  |

|---|------------------------------|----|

| 2 | Summary of benefits          |    |

| 3 | Application examples         |    |

| 4 | Multicore processing options | 7  |

| 5 | Chip features                | 9  |

| 6 | Conclusion                   |    |

| A | T4160                        |    |

| В | T4080                        | 40 |

| С | Revision history             |    |

## 2 Summary of benefits

The T4 family of processors are ideal for combined control and data plane processing. A wide variety of applications can benefit from the processing, I/O integration, and power management capabilities. Similar to other QorIQ devices, the T4 family of processors' high level of integration offers significant space, weight, and power benefits compared to multiple discrete devices. Examples include:

- Service provider networking: RNC, metro networking, gateway, core/edge router, EPC, CRAN, ATCA, and AMC solutions.

- Enterprise equipment: router, switch services, and UTM appliances.

- Data centers: NFV, SDN, ADC, WOC, UTM, proxy, server appliance, and PCI Express (PCIe) offload.

- Storage controllers: FCoE bridging, iSCSI controller, and SAN controller.

- Aerospace, defense, and government: radar imaging, ruggedized network appliance, and cockpit display.

- Industrial computing: single-board computers and test equipment.

## 2.1 e6500 CPU core

The T4 family of processors are based on the Power Architecture® e6500 core. The e6500 core uses a seven-stage pipeline for low latency response while also boosting single-threaded performance. The e6500 core also offers high aggregate instructions per clock at lower power with an innovative "fused core" approach to threading. The e6500 core's fully resourced dual threads provide 1.7 times the performance of a single thread.

The e6500 cores are clustered in banks of four cores sharing a 2 MB L2 cache, allowing efficient sharing of code and data within a multicore cluster. Each e6500 core implements the Freescale AltiVec technology SIMD engine, dramatically boosting performance of heavy math algorithms with DSP-like performance.

The e6500 core features include:

- Up to 1.8 GHz dual threaded operation

- 7 DMIPS/MHz per core

- · Advanced power saving modes, including state retention power gating

## 2.2 Virtualization

The T4 family of processors includes support for hardware-assisted virtualization. The e6500 core offers an extra core privilege level (hypervisor) and hardware offload of logical-to-real address translation. In addition, the T4 family of processors includes platform-level enhancements supporting I/O virtualization with DMA memory protection through IOMMUs and configurable "storage profiles" that provide isolation of I/O buffers between guest environments. Virtualization software for the T4 family includes kernel virtualization machine (KVM), Linux containers, and Freescale hypervisor and commercial virtualization software from vendors such as Enea®, Greenhills Software®, Mentor Graphics®, and Wind River.

## 2.3 Data Path Acceleration Architecture (DPAA)

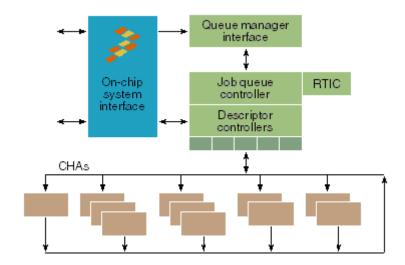

The T4 family of processors enhance the QorIQ DPAA, an innovative multicore infrastructure for scheduling work to cores (phyiscal and virtual), hardware accelerators, and network interfaces.

The Frame Manager (FMAN), a primary element of the DPAA, parses headers from incoming packets and classifies and selects data buffers with optional policing and congestion management. The FMAN passes its work to the Queue Manager (QMAN), which assigns it to cores or accelerators with a multilevel scheduling hierarchy. The T4240 processor's implementation of the DPAA offers accelerations for cryptography, enhanced regular expression pattern matching, and compression/decompression.

## 2.4 System peripherals and networking

For networking, there are dual FMANs with an aggregate of up to 16 any-speed MAC controllers that connect to PHYs, switches, and backplanes over RGMII, SGMII, QSGMII, HiGig2, XAUI, XFI, and 10Gbase-KR. The FMAN also supports new quality of service features through egress traffic shaping and priority flow control for data center bridging in converged data center networking applications. High-speed system expansion is supported through four PCI Express controllers that support varieties of lane lengths for PCIe specification 3.0, including endpoint SR-IOV with 128 virtual functions. Other peripherals include:

- SRIO

- Interlaken-LA

- SATA

- SD/MMC

- I<sup>2</sup>C

- UART

- SPI

- NOR/NAND controller

- GPIO

- 1866 MT/s DDR3/L controller

## 3 Application examples

This chip is well-suited for applications that are highly compute-intensive, I/O-intensive, or both.

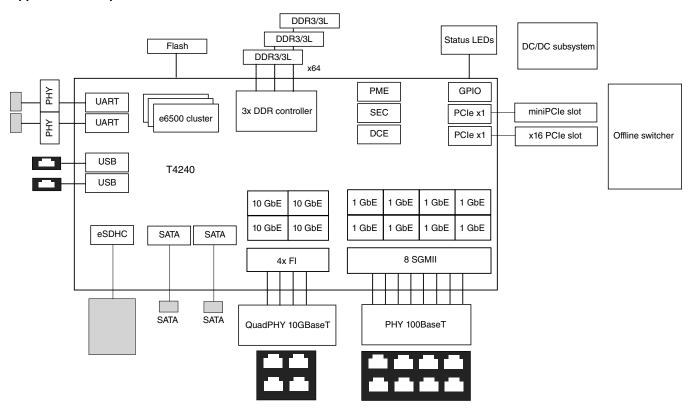

## 3.1 1U security appliance

This figure shows a 1U security appliance built around a single SoC. The QorIQ DPAA accelerates basic packet classification, filtering, and packet queuing, while the crypto accelerator (SEC 5.0), regex accelerator (PME 2.1), and compression/decompression accelerator (DCE 1.0) perform high throughput content processing. The high single threaded and aggregate DMIPS of the core CPUs provide the processing horsepower for complex classification and flow state tracking required for proxying applications as well as heuristic traffic analysis and policy enforcement.

The SoC's massive integration significantly reduces system BOM cost. SATA hard drives connect directly to the SoC's integrated controllers, and an Ethernet switch is only required if more than 16 1 GE ports or 4 10 GE ports are required. The SoC supports PCIe and Serial RapidIO for expansion.

Figure 1. SoC 1U security appliance

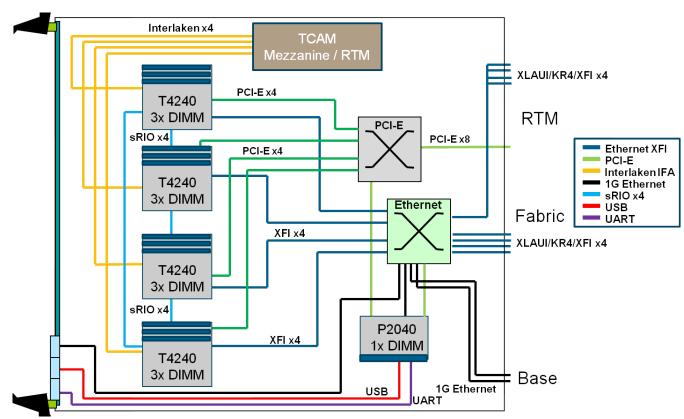

## 3.2 Rack-mounted services blade

Networking and telecom systems are frequently modular in design, built from multiple standard dimension blades, which can be progressively added to a chassis to increase interface bandwidth or processing power. ATCA is a common standard form factor for chassis-based systems.

This figure shows a potential configuration for an ATCA blade with four chips and an Ethernet switch, which provides connectivity to the front panel and backplane, as well as between the chips. Potential systems enabled by chips in ATCA style modular architectures are described below.

Application examples

Figure 2. Network services ATCA blade

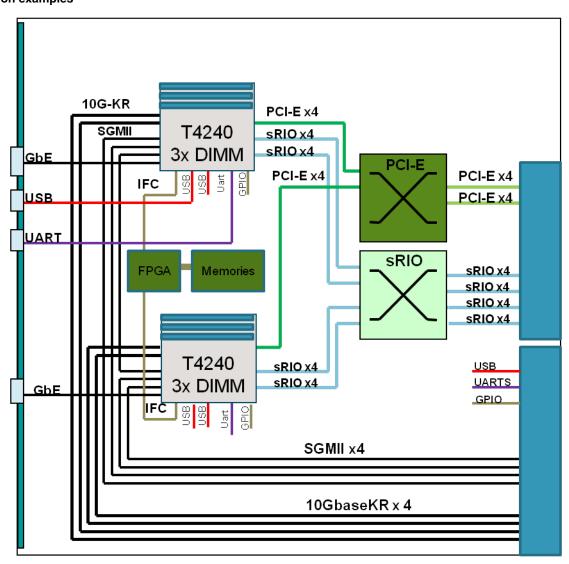

## 3.3 Radio node controller

Some of the more demanding packet-processing applications are found in the realm of wireless infrastructure. These systems have to interwork between wireless link layer protocols and IP networking protocols. Wireless protocol complexity is high, and includes scheduling, retransmission, and encryption with algorithms specific to cellular wireless access networks. Connecting to the IP network offers wireless infrastructure tremendous cost savings, but introduces all the security threats found in the IP world. The chip's network and peripheral interfaces provide it with the flexibility to connect to DSPs, and to wireless link layer framing ASICs/FPGAs (not shown). While the Data Path Acceleration Architecture offers encryption acceleration for both wireless and IP networking protocols, in addition to packet filtering capability on the IP networking side, multiple virtual CPUs may be dedicated to data path processing in each direction.

Figure 3. Radio node controller

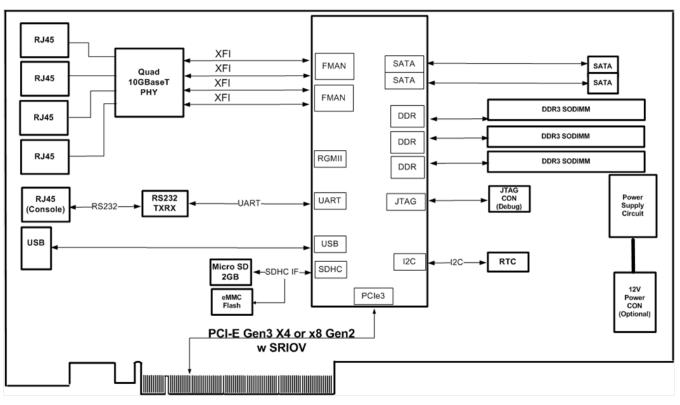

# 3.4 Intelligent network adapter

The exact form factor of this card may vary, but the concepts are similar. A chip is placed on a small form factor card with an x8 PCIe connector and multiple 10 G Ethernet ports with HighGigE support for integrating with a Trident II device. This card is then used as inline accelerator that provides both line rate networking and intelligent programmable offload from a host processor subsystem in purpose built appliances and servers, such as Open vSwitch (OVS).

This figure shows an example of a T4240 built as a PCI Express form-factor supporting virtualization through SR-IOV with quad 10 G physical networking interfaces.

**Multicore processing options**

Figure 4. Intelligent network adapter

## 4 Multicore processing options

This flexible chip can be configured to meet many system application needs. The chip's CPUs (and hardware threads as virtual CPUs) can be combined as a fully-symmetric, multiprocessing, system-on-a-chip, or they can be operated with varying degrees of independence to perform asymmetric multiprocessing. High levels of processor independence, including the ability to independently boot and reset each core, is characteristic of the chip. The ability of the cores to run different operating systems, or run OS-less, provides the user with significant flexibility in partitioning between control, datapath, and applications processing. It also simplifies consolidation of functions previously spread across multiple discrete processors onto a single device.

While up to 24 Power Architecture threads (henceforth referred to as 'virtual CPUs', or 'vCPUs') offer a large amount of total, available computing performance, raw processing power is not enough to achieve multi-Gbps data rates in high-touch networking and telecom applications. To address this, this chip enhances the Freescale Data Path Acceleration Architecture (DPAA), further reducing data plane instructions per packet, and enabling more CPU cycles to work on value-added services as opposed to repetitive, low-level tasks. Combined with specialized accelerators for cryptography, pattern matching, and compression, the chip allows the user's software to perform complex packet processing at high data rates. There are many ways to map operating systems and I/O up to 24 chip vCPUs.

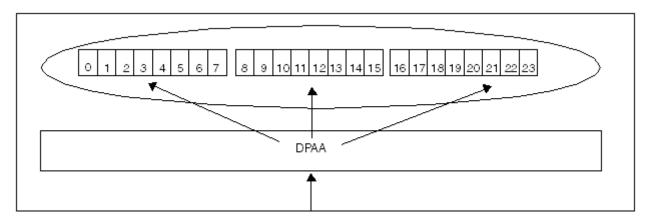

## 4.1 Asymmetric multiprocessing

As shown in this figure, the chip's vCPUs can be used in an asymmetric multi-processing model, with *n* copies of the same uni-processor OS, or *n* copies of OS 1, *n* copies of OS 2, and so on, up to 24 OS instances. The DPAA distributes work to the specific vCPUs based on basic classification or it puts work onto a common queue from which any vCPU can dequeue work.

wuncore processing options

Figure 5. 24 vCPU AMP or SMP with affinity

## 4.2 Symmetric multiprocessing

Figure 5 also presents 24 vCPU SMP, where it is typical for data processing to involve some level of task affinity.

## 4.3 Mixed symmetric and asymmetric multiprocessing

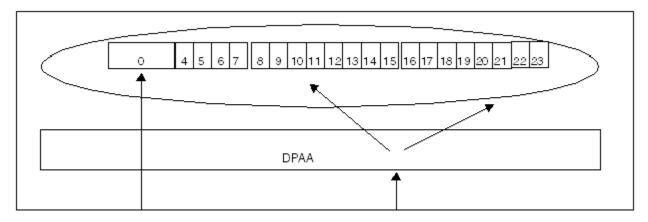

This figure shows one possibility for a mixed SMP and AMP processing. Two physical CPUs (vCPUs 0-3) are combined in an SMP cluster for control processing, with the Datapath using exact match classification to send only control packets to the SMP cluster. The remaining virtual cores could run 20 instances of datapath software.

### Figure 6. Mixed SMP and AMP option 1

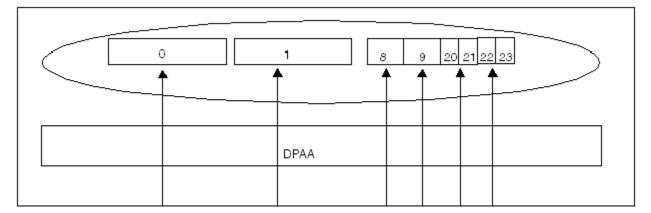

This figure shows another possibility for mixed SMP and AMP processing. Two of the physical cores are run in single threaded mode; the remaining physical cores operate as four virtual CPUs. The Datapath directs traffic to specific software partitions based on physical Ethernet port, classification, or some combination.

### Figure 7. Mixed SMP and AMP option 2

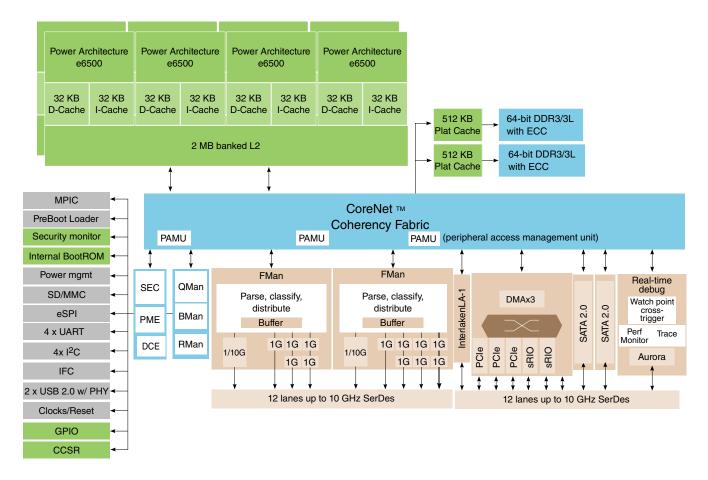

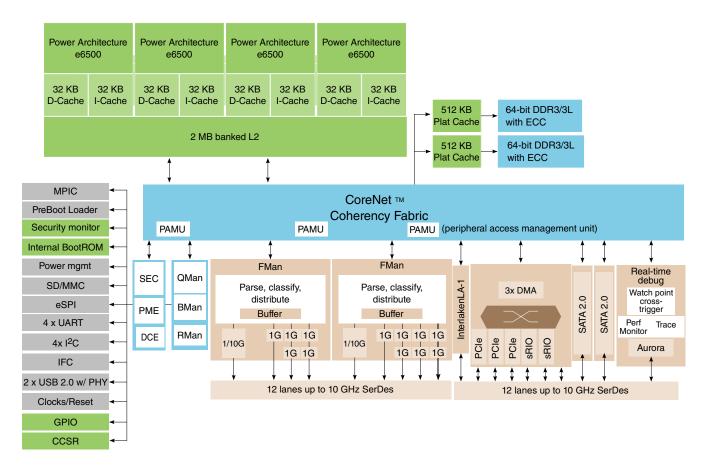

# 5 Chip features

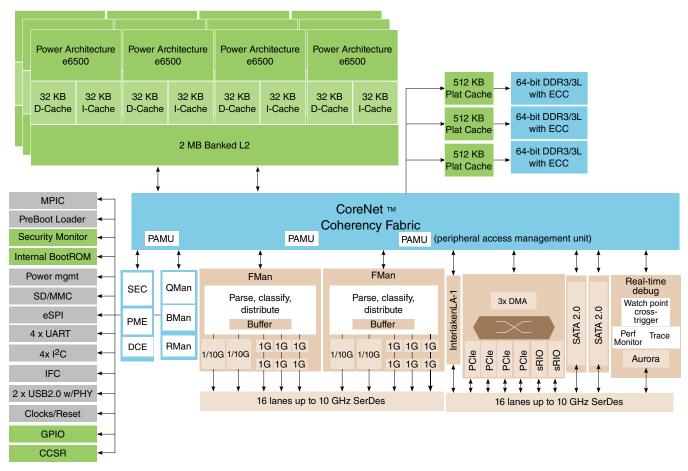

This section describes the key features and functionalities of the T4240 chip. See the T4160 and T4080 appendices for those device's specific block diagrams.

## 5.1 Block diagram

This figure shows the major functional units within the chip.

#### Crip features

### Figure 8. T4240 block diagram

### 5.2 Features summary

This chip includes the following functions and features:

- 12, dual-threaded e6500 cores for a total of 24/16/8 threads (T4240/T4160/T4080) built on Power Architecture® technology

- Arranged as three clusters of four cores sharing a 2 MB L2 cache, 6 MB L2 cache total.

- Up to 1.8 GHz with 64-bit ISA support (Power Architecture v2.06-compliant)

- Three privilege levels of instruction: user, supervisor, and hypervisor

- Up to 1.5 MB CoreNet Platform Cache (CPC)

- Hierarchical interconnect fabric

- CoreNet fabric supporting coherent and non-coherent transactions with prioritization and bandwidth allocation amongst CoreNet end-points

- 1.46 Tbps coherent read bandwidth

- Up to three 64-bit DDR3/3L SDRAM memory controllers with ECC and interleaving support

- Up to 1.867 GT/s data transfer rate

- 64 GB per DDR controller

- Data Path Acceleration Architecture (DPAA) incorporating acceleration for the following functions:

- Packet parsing, classification, and distribution (Frame Manager 1.1) up to 50 Gbps

- Queue management for scheduling, packet sequencing, and congestion management (Queue Manager 1.1)

- Queue Manager (QMan) fabric supporting packet-level queue management and quality of service scheduling

- Hardware buffer management for buffer allocation and de-allocation (BMan 1.1)

- Cryptography acceleration (SEC 5.0) at up to 40 Gbps

- RegEx Pattern Matching Acceleration (PME 2.1) at up to 10 Gbps

- Decompression/Compression Acceleration (DCE 1.0) at up to 20 Gbps

- DPAA chip-to-chip interconnect via RapidIO Message Manager (RMAN 1.0)

- Up to 32 SerDes lanes at up to 10.3125 GHz

- Ethernet interfaces

- Up to four 10 Gbps Ethernet XAUI or 10GBase-KR XFI MACs

- Up to sixteen 1 Gbps Ethernet MACs

- Up to two 1Gbps Ethernet RGMII MACs

- Maximum configuration of 4 x 10 GE (XFI) + 10 x 1 GE (SGMII) + 2 x 1 GE (RGMII)

- High-speed peripheral interfaces

- Up to four PCI Express 2.0 controllers, two supporting 3.0

- Two Serial RapidIO 2.0 controllers/ports running at up to 5 GHz with Type 11 messaging and Type 9 data streaming support

- Interlaken look-aside interface for serial TCAM connection at 6.25 and 10.3125 Gbps per-lane rates.

- Additional peripheral interfaces

- Two serial ATA (SATA 2.0) controllers

- Two high-speed USB 2.0 controllers with integrated PHY

- Enhanced secure digital host controller (SD/MMC/eMMC)

- Enhanced serial peripheral interface (eSPI)

- Four I2C controllers

- Four 2-pin or two 4-pin UARTs

- Integrated Flash controller supporting NAND and NOR flash

- Three eight-channel DMA engines.

- · Support for hardware virtualization and partitioning enforcement

- QorIQ Platform's Trust Architecture 2.0

## 5.3 Critical performance parameters

This table lists key performance indicators that define a set of values used to measure SoC operation.

#### Table 1. Critical performance parameters

| Indicator                            | Values(s)                                                                                   |

|--------------------------------------|---------------------------------------------------------------------------------------------|

| Top speed bin core frequency         | 1.8 GHz                                                                                     |

| Maximum memory data rate             | 1867 MHz (DDR3) <sup>1</sup> , 1600 MHz for DDR3L<br>• 1.5 V for DDR3<br>• 1.35 V for DDR3L |

| Integrated flash controller (IFC)    | 1.8 V                                                                                       |

| Operating junction temperature range | 0-105 C                                                                                     |

| Package                              | 1932-pin, flip-chip plastic ball grid array (FC-PBGA), 45 x 45mm                            |

1. Conforms to JEDEC standard

## 5.4 Core and CPU clusters

This chip offers 12, high-performance, 64-bit Power Architecture, Book E-compliant cores. Each CPU core supports two hardware threads, which software views as a virtual CPU. The core CPUs are arranged in clusters of four with a shared 2 MB L2 cache.

#### Crip features

This table shows the computing metrics the core supports.

#### Table 2. Power architecture metrics

| Metric                  | Per core | Per cluster | Full device |

|-------------------------|----------|-------------|-------------|

| DMIPS                   | 10,800   | 43,200      | 129,600     |

| Single-precision GFLOPs | 18       | 72          | Up to 216   |

| Double-precision GFLOPs | 3.6      | 14.4        | Up to 42.4  |

The core subsystem includes the following features:

- Up to 1.8 GHz

- Dual-thread with simultaneous multi-threading (SMT)

- Threading can be disabled on a per CPU basis

- 40-bit physical addressing

- L2 MMU

- Supporting 4 KB pages

- TLB0; 8-way set-associative, 1024-entries (4 KB pages)

- TLB1; fully associative, 64-entry, supporting variable size pages and indirect page table entries

- Hardware page table walk

- 64-byte cache line size

- L1 caches, running at core frequency

- 32 KB instruction, 8-way set-associative

- 32 KB data, 8-way set-associative

- Each with data and tag parity protection

- Hardware support for memory coherency

- Five integer units: 4 simple (2 per thread), 1 complex (integer multiply and divide)

- Two load-store units: one per thread

- Classic double-precision floating-point unit

- Uses 32 64-bit floating-point registers (FPRs) for scalar single- and double-precision floating-point arithmetic

- Designed to comply with IEEE Std. 754<sup>™</sup>-1985 FPU for both single and double-precision operations

- AltiVec unit

- 128-bit Vector SIMD engine

- 32 128-bit VR registers

- Operates on a vector of

- Four 32-bit integers

- Four 32-bit single precision floating-point units

- Eight 16-bit integers

- Sixteen 8-bit integers

- Powerful permute unit

- Enhancements include: Move from GPRs to VR, sum of absolute differences operation, extended support for misaligned vectors, handling head and tails of vectors

- Supports Data Path Acceleration Architecture (DPAA) data and context "stashing" into L1 and L2 caches

- User, supervisor, and hypervisor instruction level privileges

- Addition of Elemental Barriers and "wait on reservation" instructions

- New power-saving modes including "drowsy core" with state retention and nap

- State retention power-saving mode allows core to quickly wake up and respond to service requests

- Processor facilities

- Hypervisor APU

- "Decorated Storage" APU for improved statistics support

- Provides additional atomic operations, including a "fire-and-forget" atomic update of up to two 64-bit quantities by a single access

- Addition of Logical to Real Address translation mechanism (LRAT) to accelerate hypervisor performance

- Expanded interrupt model

- Improved Programmable Interrupt Controller (PIC) automatically ACKs interrupts

- Implements message send and receive functions for interprocessor communication, including receive filtering

- External PID load and store facility

- Provides system software with an efficient means to move data and perform cache operations between two disjoint address spaces

- Eliminates the need to copy data from a source context into a kernel context, change to destination address space, then copy the data to the destination address space or alternatively to map the user space into the kernel address space

Details of the banked L2 are provided below.

- 2 MB cache with ECC protection (data, tag, & status)

- Pipelined data array access with 2 cycle repeat rate

- 4 banks, supporting up to four concurrent accesses.

- 64-byte cache line size

- 16 way, set associative

- Ways in each bank can be configured in one of several modes

- Flexible way partitioning per vCPU

- I-only, D-only, or unified

- Supports direct stashing of datapath architecture data into L2

The chip also contains up to 1.5 MB of shared L3 CoreNet Platform Cache (CPC), with the following features:

- Total 1.5 MB, implemented as three 512 KB arrays, one per DDR controller

- ECC protection for Data, Tag and Status

- 16-way set associative with configurable replacement algorithms

- Allocation control for data read, data store, castout, decorated read, decorated store, instruction read and stash

- Configurable SRAM partitioning

## 5.5 Inverted cache hierarchy

From the perspective of software running on an core vCPU, the SoC incorporates a 2.5-level cache hierarchy. These levels are as follows:

- Level 1: Individual core 32 KB Instruction and Data caches

- Level 2: Locally banked 2 MB cache (configurably shared by other vCPUs in the cluster)

- Level 2.5: Remote banked 2 MB caches (total 4 MB)

When vCPUs in different physical clusters are part of the same coherency domain, the CoreNet Coherency Fabric causes any cache miss in the vCPU's local L2 to be snooped by the remote L2s belonging to the other clusters. On a hit in a remote L2, the associated data is returned directly to the requesting vCPU, eliminating the need for a higher latency flush and retry protocol. This direct cache transfer is called cache intervention.

Previous generation QorIQ products also support cache intervention from their private backside L2 caches; however, the SoC's allocation policies make greater use of intervention. The sum of the SoC's L2 caches are 3x larger than the CPC. Ttherefore, the CPC is not intended to act as backing store for the L2s, as it typically is in the previous generation. This allows the CPCs to be dedicated to the non-CPU masters in the SoC, storing DPAA data structures and IO data that the CPUs and accelerators will most likely need.

Although the SoC supports allocation policies that would result in CPU instructions and in data being held in the CPC (CPC acting as vCPU L3), this is not the default. Because the CPC serves fewer masters, it serves those masters better, by reducing the DDR bandwidth consumed by the DPAA and improving the average latency.

## 5.6 CoreNet fabric and address map

The CoreNet fabric provides the following:

- A highly concurrent, fully cache coherent, multi-ported fabric

- Point-to-point connectivity with flexible protocol architecture allows for pipelined interconnection between CPUs, platform caches, memory controllers, and I/O and accelerators at up to 733 MHz

- The CoreNet fabric has been designed to overcome bottlenecks associated with shared bus architectures, particularly address issue and data bandwidth limitations. The chip's multiple, parallel address paths allow for high address bandwidth, which is a key performance indicator for large coherent multicore processors.

- Eliminates address retries, triggered by CPUs being unable to snoop within the narrow snooping window of a shared bus. This results in the chip having lower average memory latency.

This chip's 40-bit, physical address map consists of local space and external address space. For the local address map, 32 local access windows (LAWs) define mapping within the local 40-bit (1 TB) address space. Inbound and outbound translation windows can map the chip into a larger system address space such as the RapidIO or PCIe 64-bit address environment. This functionality is included in the address translation and mapping units (ATMUs).

## 5.7 Memory complex

The SoC's memory complex consists of up to three DDR controllers for main memory, and the memory controllers associated with the Integrated Flash Controller (IFC).

## 5.7.1 DDR memory controllers

The chip offers up to three 64-bit DDR controllers supporting ECC protected memories. These DDR controllers operate at up to 1.867 GT/s for DDR3, and, in more power sensitive applications, up to 1.6 GHz for DDR3L. Some key DDR controller features are as follows:

- Interleaving options

- None, three fully independent controllers

- · Two interleaved, one independent

- Three interleaved

- Interleaving can be configured on 1 KB, 4 KB, and 8 KB granules

- Support x4, x8, and x16 memory widths

- Programmable support for single, dual, and quad ranked devices and modules

- · Support for both unbuffered and registered DIMMs

- 4 chip-selects per controller

- 64 GB per controller, 192 GB per chip

- The SoC can be configured to retain the currently active SDRAM page for pipelined burst accesses. Page mode support of up to 64 simultaneously open pages can dramatically reduce access latencies for page hits. Depending on the memory system design and timing parameters, page mode can save up to ten memory clock cycles for subsequent burst accesses that hit in an active page.

- Using ECC, the SoC detects and corrects all single-bit errors and detects all double-bit errors and all errors within a nibble.

- Upon detection of a loss of power signal from external logic, the DDR controllers can put compliant DDR SDRAM DIMMs into self-refresh mode, allowing systems to implement battery-backed main memory protection.

- In addition, the DDR controllers offer an initialization bypass feature for use by system designers to prevent reinitialization of main memory during system power-on after an abnormal shutdown.

- Support active zeroization of system memory upon detection of a user-defined security violation.

### 5.7.1.1 DDR bandwidth optimizations

Multicore SoCs are able to increase CPU and network interface bandwidths faster than commodity DRAM technologies are improving. As a result, it becomes increasingly important to maximize utilization of main memory interfaces to avoid a memory bottleneck. The T4 family's DDR controllers are Freescale-developed IP, optimized for the QorIQ SoC architecture, with the goal of improving DDR bandwidth utilization by fifty percent when compared to first generation QorIQ SoCs.

Most of the WRITE bandwidth improvement and approximately half of the READ bandwidth improvement is met through target queue enhancements; in specific, changes to the scheduling algorithm, improvements in the bank hashing scheme, support for more transaction re-ordering, and additional proprietary techniques.

The remainder of the READ bandwidth improvement is due to the addition of an intelligent data prefetcher in the memory subsystem.

### 5.7.1.2 Prefetch Manager (PMan)

#### NOTE

All transactions to DDR pass through the CPC; this means the CPC can miss (and trigger prefetching) even on data that is not intended for allocation into the CPC.

The PMAN monitors CPC misses for opportunities to prefetch, using a "confidence"-based algorithm to determine its degree of aggressiveness. It can be configured to monitor multiple memory regions (each of different size) for prefetch opportunities. Multiple CPC misses on accesses to a tracked region for consecutive cache blocks increases confidence to start prefetching, and a CPC miss of a tracked region with same stride will instantly cause prefetching.

The PMan uses feedback to increase or decrease its aggressiveness. When the data it prefetches is being used, it prefetches further ahead. If the request stride length changes or previously prefetched data isn't consumed, prefetching slows or stops (at least for that region/requesting device/transaction type).

### 5.7.2 PreBoot Loader and nonvolatile memory interfaces

The PreBoot Loader (PBL) operates similarly to an I<sup>2</sup>C boot sequencer but on behalf of a large number of interfaces.

It supports IFC, I<sup>2</sup>C, eSPI, eSDHC.

The PBL's functions include the following:

- · Simplifies boot operations, replacing pin strapping resistors with configuration data loaded from nonvolatile memory

- Uses the configuration data to initialize other system logic and to copy data from low speed memory interfaces (I<sup>2</sup>C, IFC, eSPI, and SD/MMC) into fully initialized DDR or the 2 MB front-side cache

### 5.7.2.1 Integrated Flash Controller

The SoC incorporates an Integrated Flash Controller similar to the one used in some previous generation QorIQ SoCs. The IFC supports both NAND and NOR flash, as well as a general purpose memory mapped interface for connecting low speed ASICs and FPGAs.

### 5.7.2.1.1 NAND Flash features

- x8/x16 NAND Flash interface

- Optional ECC generation/checking

- Flexible timing control to allow interfacing with proprietary NAND devices

- SLC and MLC Flash devices support with configurable page sizes of up to 4 KB

- · Support advance NAND commands like cache, copy-back, and multiplane programming

#### unp features

- Boot chip-select (CS0) available after system reset, with boot block size of 8 KB, for execute-in-place boot loading from NAND Flash

- Up to terabyte Flash devices supported

### 5.7.2.1.2 NOR Flash features

- Data bus width of 8/16/32

- Compatible with asynchronous NOR Flash

- Directly memory mapped

- Supports address data multiplexed (ADM) NOR device

- · Flexible timing control allows interfacing with proprietary NOR devices

- Boot chip-select (CS0) available at system reset

### 5.7.2.1.3 General-purpose chip-select machine (GPCM)

The IFC's GPCM supports the following features:

- Normal GPCM

- Support for x8/16/32-bit device

- · Compatible with general purpose addressable device, for example, SRAM and ROM

- External clock is supported with programmable division ratio (2, 3, 4, and so on, up to 16)

- Generic ASIC Interface

- Support for x8/16/32-bit device

- Address and Data are shared on I/O bus

- Following address and data sequences are supported on I/O bus:

- 32-bit I/O: AD

- 16-bit I/O: AADD

- 8-bit I/O: AAAADDDD

### 5.7.2.2 Serial memory controllers

In addition to the parallel NAND and NOR flash supported by the IFC, the SoC supports serial flash using eSPI, I<sup>2</sup>C and SD/MMC/eMMC card and device interfaces. The SD/MMC/eMMC controller includes a DMA engine, allowing it to move data from serial flash to external or internal memory following straightforward initiation by software.

Detailed features of the eSDHC include the following:

- Conforms to the SD Host Controller Standard Specification version 2.0, including Test event register support

- Compatible with the MMC System Specification version 4.2

- Compatible with the SD Memory Card Specification version 2.0, and supports the high capacity SD memory card

- Designed to work with SD memory, SD combo, MMC, and their variants like mini and micro.

- Card bus clock frequency up to 52 MHz

- Supports 1-/4-bit SD, 1-/4-/8-bit MMC modes

- Supports single-block and multi-block read, and write data transfer

- Supports block sizes of 1-2048 bytes

- Supports the mechanical write protect detection. In the case where write protect is enabled, the host will not initiate any write data command to the card

- · Supports both synchronous and asynchronous abort

- Supports pause during the data transfer at block gap

- Supports Auto CMD12 for multi-block transfer

- · Host can initiate command that do not use data lines, while data transfer is in progress

- Embodies a configurable 128x32-bit FIFO for read/write data

- Supports SDMA, ADMA1, and ADMA2 capabilities

- Supports external SD bus voltage selection by register configuration

- Host will send 80 idle SD clock cycles to card, which are needed during card power-up, if bit INITA in the system control register (SYSCTL) is set

## 5.8 Universal serial bus (USB) 2.0

The two USB 2.0 controllers with integrated PHY provide point-to-point connectivity that complies with the USB specification, Rev. 2.0. Each of the USB controllers with integrated PHY can be configured to operate as a stand-alone host, and one of the controllers (USB #2) can be configured as a stand-alone device, or with both host and device functions operating simultaneously.

## 5.9 High-speed peripheral interface complex (HSSI)

This chip offers a variety of high-speed serial interfaces, sharing a set of 16 SerDes lanes. Each interface is backed by a high speed serial interface controller. This chip has the following types and quantities of controllers:

- Four 2.0 PCI Express controllers, two supporting 3.0

- Two Serial RapidIO 2.0

- Two SATA 2.0

- One Interlaken look-aside

- Aurora

- · Up to sixteen Ethernet controllers with various protocols

## 5.9.1 PCI Express

Each of the chip's PCI Express controllers is compliant with the PCI Express Base Specification Revision 2.0. Two are additionally compliant with Revision 3.0 (8 GHz). Key features of each PCI Express controller include the following:

- Power-on reset configuration options allow root complex or endpoint functionality.

- The physical layer operates at 2.5, 5, or 8 Gbaud data rate per lane.

- x4, x2, and x1 link widths supported on all controllers

- Two controllers can support x8 link width

- Both 32- and 64-bit addressing

- 256-byte maximum payload size

- Full 64-bit decode with 40-bit wide windows

- Inbound INTx transactions

- Message signaled interrupt (MSI) transactions

- · One PCI Express controller supports end-point SR-IOV

- Two physical functions, each with 64 virtual functions

- Eight MSI-X per virtual function

## 5.9.2 Serial RapidIO

The Serial RapidIO interface is based on the *RapidIO Interconnect Specification, Revision 2.1*. RapidIO is a high-performance, point-to-point, low-pin-count, packet-switched system-level interconnect that can be used in a variety of applications as an open standard. The rich feature set includes high data bandwidth, low-latency capability, and support for high-performance I/O devices as well as message-passing and software-managed programming models. Receive and transmit ports operate independently, and with 2 x 4 Serial RapidIO controllers, the aggregate theoretical bandwidth is 32 Gbps.

The chip offers two Serial RapidIO controllers, muxed onto the SerDes blocks. The Serial RapidIO interface is based on the *RapidIO Interconnect Specification, Revision 2.1*. Receive and transmit ports operate independently and with 2 x 4 Serial RapidIO controllers; the aggregate theoretical bandwidth is 32 Gbps. The Serial RapidIO controllers can be used in conjunction with "Rapid IO Message Manager (RMAN), as described in RapidIO Message Manager (RMAn)."

Key features of the Serial RapidIO interface unit include the following:

- Support for RapidIO Interconnect Specification, Revision 2.1 (All transaction flows and priorities.)

- 2x, and 4x LP-serial link interfaces, with transmission rates of 2.5, 3.125, or 5.0 Gbaud (data rates of 1.0, 2.0, 2.5, or 4.0 Gbps) per lane

- Auto-detection of 1x, 2x, or 4x mode operation during port initialization

- 34-bit addressing and up to 256-byte data payload

- Support for SWRITE, NWRITE, NWRITE\_R and Atomic transactions

- Receiver-controlled flow control

- RapidIO error injection

- · Internal LP-serial and application interface-level loopback modes

The Serial RapidIO controller also supports the following capabilities, many of which are leveraged by the RMan to efficient chip-to-chip communication through the DPAA:

- Support for RapidIO Interconnect Specification 2.1, "Part 2: Message Passing Logical Specification"

- Supports RapidIO Interconnect Specification 2.1, "Part 10: Data Streaming Logical Specification"

- Supports RapidIO Interconnect Specification 2.1, "Annex 2: Session Management Protocol"

Supports basic stream management flow control (XON/XOFF) using extended header message format

- Up to 16 concurrent inbound reassembly operations

- One additional reassembly context is reservable to a specific transaction type

- Support for outbound Type 11 messaging

- Support for outbound Type 5 NWRITE and Type 6 SWRITE transactions

- Support for inbound Type 11 messaging

- Support for inbound Type 9 data streaming transactions

- Support for outbound Type 9 data streaming transactions

- Up to 64 KB total payload

- Support for inbound Type 10 doorbell transactions

- Transaction steering through doorbell header classification

- Support for outbound Type 10 doorbell transactions

- Ordering can be maintained with respect to other types of traffic.

- Support for inbound and outbound port-write transactions

- Data payloads of 4 to 64 bytes

### 5.9.3 SATA

Each of the SoC's two SATA controllers is compliant with the *Serial ATA 2.6 Specification*. Each of the SATA controllers has the following features:

- Supports speeds: 1.5 Gbps (first-generation SATA), and 3Gbps (second-generation SATA )

- Supports advanced technology attachment packet interface (ATAPI) devices

- Contains high-speed descriptor-based DMA controller

- Supports native command queuing (NCQ) commands

- Supports port multiplier operation

- Supports hot plug including asynchronous signal recovery

### 5.9.4 Interlaken Look-Aside Controller (LAC) and interface

Interlaken Look-Aside is a high speed serial channelized chip-to-chip interface. To facilitate interoperability between a GPU or NPU and a look-aside co-processor, the Interlaken Look-Aside protocol is defined for short transaction with small data & command transfers. Although based on the Interlaken protocol, Interlaken Look-Aside is not directly compatible with the Interlaken streaming specification, and can be considered a different operational mode. The SoC's Interlaken LAC is Look-Aside only.

The Interlaken LAC features:

- Supports Interlaken Look-Aside Protocol definition, Rev. 1.1

- Supports up to 32 software portals, with stashing option

- Supports inband per-channel flow control options, with a simple xon/xoff semantics

- Supports a range of SerDes frequencies ( 6.25 GHz to 10.3125 GHz) and widths (x4, x8)

- 64B/67B data encoding and scrambling

- Programmable BURSTMAX (256 to 512-byte) and BURSTSHORT (8 to 16 bytes)

- Error detection: illegal burst sizes, bad 64/67 word type, CRC-24 error, receiver data overflow

- Built in statistics and error counters

- · Dynamic power-down of each software portal

Although not part of the DPAA, the LAC leverages DPAA concepts, including software portals and stashing. Each vCPU has a private software portal into the LAC, through which it issues commands and receives its results. Software commands to the LAC commands are translated into the Interlaken control words and data words, which are transmitted across the SerDes lanes to the co-processor, generally expected to be a TCAM.

TCAM responses received by the LAC (control words and data words) are then written to memory mapped space defined for the software portal of the vCPU that initiated the request. These writes can be configured to stash data directly into the vCPU's cache to reduce latency.

Each vCPU can generally have four outstanding transactions with the LAC; however, if not all vCPUs are configured to use the LAC, those that are configured can have more outstanding transactions. Order is maintained for all transactions issued by a single portal.

## 5.10 Data Path Acceleration Architecture (DPAA)

This chip includes an enhanced implementation of the QorIQ Datapath Acceleration Architecture (DPAA). This architecture provides the infrastructure to support simplified sharing of networking interfaces and accelerators by multiple CPUs. These resources are abstracted as enqueue/dequeue operations by CPU 'portals' into the datapath. Beyond enabling multicore sharing of resources, the DPAA significantly reduces software overheads associated with high-touch packet-processing operations.

Examples of the types of packet-processing services that this architecture is optimized to support are as follows:

- Traditional routing and bridging

- Firewall

- · Security protocol encapsulation and encryption

The functions off-loaded by the DPAA fall into two broad categories:

- · Packet distribution and queue-congestion management

- Accelerating content processing

## 5.10.1 Packet distribution and queue/congestion management

This table lists some packet distribution and queue/congestion management offload functions.

### Table 3. Offload functions

| Function type             | Definition                                                                                                                                                                                                                                                                                                                                                                             |

|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data buffer<br>management | Supports allocation and deallocation of buffers belonging to pools originally created by software with configurable depletion thresholds. Implemented in a module called the Buffer Manager (BMan).                                                                                                                                                                                    |

| Queue<br>management       | Supports queuing and quality-of-service scheduling of frames to CPUs, network interfaces and DPAA logic blocks, maintains packet ordering within flows. Implemented in a module called the Queue Manager (QMan). The QMan, besides providing flow-level queuing, is also responsible for congestion management functions such as RED/WRED, congestion notifications and tail discards. |

| Packet distribution       | Supports in-line packet parsing and general classification to enable policing and QoS-based packet distribution to the CPUs for further processing of the packets. This function is implemented in the block called the Frame Manager (FMan).                                                                                                                                          |

| Policing                  | Supports in-line rate-limiting by means of two-rate, three-color marking (RFC 2698). Up to 256 policing profiles are supported. This function is also implemented in the FMan.                                                                                                                                                                                                         |

| Egress Scheduling         | Supports hierarchical scheduling and shaping, with committed and excess rates. This function is supported in the QMan, although the FMan performs the actual transmissions.                                                                                                                                                                                                            |

### 5.10.2 Accelerating content processing

Properly implemented acceleration logic can provide significant performance advantages over most optimized software with acceleration factors on the order of 10-100x. Accelerators in this category typically touch most of the bytes of a packet (not just headers). To avoid consuming CPU cycles in order to move data to the accelerators, these engines include well-pipelined DMAs. This table lists some specific content-processing accelerators on the chip.

| Table 4. | <b>Content-processing accelerators</b> |

|----------|----------------------------------------|

|----------|----------------------------------------|

| Interface                                                       | Definition                                                                                     |  |

|-----------------------------------------------------------------|------------------------------------------------------------------------------------------------|--|

| SEC                                                             | Crypto-acceleration for protocols such as IPsec, SSL, and 3GPP RLC                             |  |

| PME                                                             | Regex style pattern matching for unanchored searches, including cross-packet stateful patterns |  |

| DCE Compression/Decompression acceleration for ZLib and deflate |                                                                                                |  |

## 5.10.3 Enhancements of T4240 compared to first generation DPAA

A short summary of T4240 enhancements over the first generation DPAA (as implemented in the P4080) is provided below:

- Frame Manager

- 2x performance increase (up to 25 Gbps per FMan)

- Storage profiles.

- HiGig (3.125 GHz) and HiGig2 (3.125 GHz and 3.75 GHz)

- Energy Efficient Ethernet

- SEC 5.0

- 2x performance increase for symmetric encryption and protocol processing

- Up to 20 Gbps for IPsec @ Imix

- 10x performance increase for public key algorithms

- Support for 3GPP Confidentiality and Integrity Algorithms 128-EEA3 & 128-EIA3 (ZUC)

- DCE 1.0, new accelerator for compression/decompression

- RMan (Serial RapidIO Manager)

- DPAA overall capabilities

- Data Center Bridging

- Egress Traffic Shaping

## 5.10.4 DPAA terms and definitions

The QorIQ Platform's Data Path Acceleration Architecture (henceforth DPAA) assumes the existence of network flows, where a flow is defined as a series of network datagrams, which have the same processing and ordering requirements. The DPAA prescribes data structures to be initialized for each flow. These data structures define how the datagrams associated with that flow move through the DPAA. Software is provided a consistent interface (the software portal) for interacting with hardware accelerators and network interfaces.

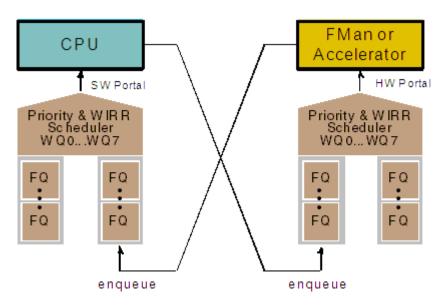

All DPAA entities produce data onto frame queues (a process called enqueuing) and consume data from frame queues (dequeuing). Software enqueues and dequeues through a software portal (each vCPU has two software portals), and the FMan, RMan, and DPAA accelerators enqueue/dequeue through hardware portals. This figure illustrates this key DPAA concept.

This table lists common DPAA terms and their definitions.

#### Table 5. DPAA terms and definitions

| Term   | Definition                                                                   | Graphic representation |

|--------|------------------------------------------------------------------------------|------------------------|

| Buffer | Region of contiguous memory, allocated by software, managed by the DPAA BMan | в                      |

Table continues on the next page ...

ump features

| Term                | Definition                                                                                                                                                    | Graphic representation                         |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|

| Buffer pool         | Set of buffers with common characteristics (mainly size, alignment, access control)                                                                           | ВВВ                                            |

| Frame               | Single buffer or list of buffers that hold data, for example, packet payload, header, and other control information                                           |                                                |

| Frame queue<br>(FQ) | FIFO of frames                                                                                                                                                | FQ = F F                                       |

| Work queue<br>(WQ)  | FIFO of FQs                                                                                                                                                   | WQ = FQ FQ                                     |

| Channel             | Set of eight WQs with hardware provided prioritized access                                                                                                    | $Chan = \frac{0  FQ  FQ}{7  FQ  FQ}  Priority$ |

| Dedicated channel   | Channel statically assigned to a particular end point, from which<br>that end point can dequeue frames. End point may be a CPU,<br>FMan, PME,DCE,RMan or SEC. | -                                              |

| Pool channel        | A channel statically assigned to a group of end points, from which<br>any of the end points may dequeue frames.                                               |                                                |

#### Table 5. DPAA terms and definitions (continued)

### 5.10.5 Major DPAA components

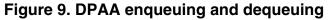

The SoC's Datapath Acceleration Architecture, shown in the figure below, includes the following major components:

- Frame Manager (FMan)

- Queue Manager (QMan)

- Buffer Manager (BMan)

- RapidIO Message Manager (RMan 1.0)

- Security Engine (SEC 5.0)

- Pattern Matching Engine (PME 2.1)

- Decompression and Compression Engine (DCE 1.0)

The QMan and BMan are infrastructure components, which are used by both software and hardware for queuing and memory allocation/deallocation. The Frame Managers and RMan are interfaces between the external world and the DPAA. These components receive datagrams via Ethernet or Serial RapidIO and queue them to other DPAA entities, as well as dequeue datagrams from other DPAA entities for transmission. The SEC, PME, and DCE are content accelerators that dequeue processing requests (typically from software) and enqueue results to the configured next consumer. Each component is described in more detail in the following sections.

This figure is a logical view of the DPAA.

Figure 10. Logical representation of DPAA

### 5.10.5.1 Frame Manager and network interfaces

The chip incorporates two enhanced Frame Managers. The Frame Manager improves on the bandwidth and functionality offered in the P4080.

Each Frame Manager, or FMan, combines Ethernet MACs with packet parsing and classification logic to provide intelligent distribution and queuing decisions for incoming traffic. Each FMan supports PCD at 37.2 Mpps, supporting line rate 2x10G + 2x2.5G at minimum frame size.

These Ethernet combinations are supported:

- 10 Gbps Ethernet MACs are supported with XAUI (four lanes at 3.125 GHz) or XFI (one lane at 10.3125 GHz SerDes).

- 1 Gbps Ethernet MACs are supported with SGMII (one lane at 1.25 GHz with 3.125 GHz option for 2.5 Gbps Ethernet).

- SGMIIs can be run at 3.125 GHz so long as the total Ethernet bandwidth does not exceed 25 Gbps on the associated FMan.

- If not already assigned to SGMII, two MACs can be used with RGMII.

- Four x1Gbps Ethernet MACs can be supported using a single lane at 5 GHz (QSGMII).

- HiGig is supported using four lanes at 3.125 GHz or 3.75 GHz (HiGig2).

The Frame Manager's Ethernet functionality also supports the following:

- 1588v2 hardware timestamping mechanism in conjunction with IEEE Std. 802.3bf (Ethernet support for time synchronization protocol)

- Energy Efficient Ethernet (IEEE Std. 802.3az)

- IEEE Std. 802.3bd (MAC control frame support for priority based flow control)

- IEEE Std. 802.1Qbb (Priority-based flow control) for up to eight queues/priorities

- IEEE Std. 802.1Qaz (Enhanced transmission selection) for three or more traffic classes

### 5.10.5.1.1 Receiver functionality: parsing, classification, and distribution

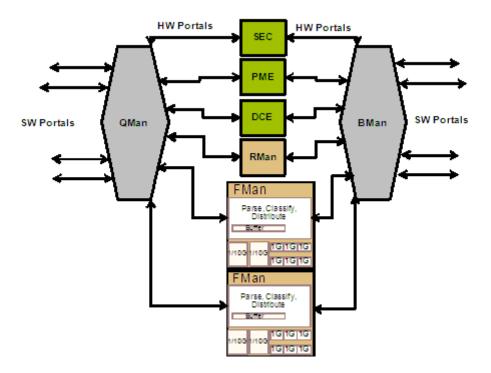

Each Frame Manager matches its 25 Gbps Ethernet connectivity with 25 Gbps (37.2 Mpps) of Parsing, Classification, and Distribution (PCD) performance. PCD is the process by which the Frame Manager identifies the frame queue on which received packets should be enqueued. The consumer of the data on the frame queues is determined by Queue Manager configuration; however, these activities are closely linked and managed by the FMan Driver and FMan Configuration Tool, as in previous QorIQ SoCs.

This figure provides a logical view of the FMan's processing flow, illustrating the PCD features.

### Figure 11. Logical view of FMan processing

Each frame received by the FMan is buffered internally while the Parser, KeyGen, and Classification functions operate.

The parse function can parse many standard protocols, including options and tunnels, and it supports a generic configurable capability to allow proprietary or future protocols to be parsed. Hard parsing of the standard protocol headers can be augmented with user-defined soft parsing rules to handle proprietary header fields. Hard and soft parsing occurs at wire speed.

This table defines several types of parser headers.

| Table 6. | Parser header types | \$ |

|----------|---------------------|----|

|----------|---------------------|----|

| Header type             | Definition                                                                                                                                                                                                                        |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Self-describing         | Announced by proprietary values of Ethertype, protocol identifier, next header, and other standard fields. They are self-describing in that the frame contains information that describes the presence of the proprietary header. |

| Non-self-<br>describing | Does not contain any information that indicates the presence of the header.                                                                                                                                                       |

Table continues on the next page...

| Table 6. | Parser header types (continued) |  |

|----------|---------------------------------|--|

|          |                                 |  |

| Header type | Definition                                                                                                                                                                                                                        |  |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|             | For example, a frame that always contains a proprietary header before the Ethernet header would be non-self-describing. Both self-describing and non-self-describing headers are supported by means of parsing rules in the FMan. |  |

| Proprietary | Can be defined as being self-describing or non-self-describing                                                                                                                                                                    |  |

The underlying notion is that different frames may require different treatment, and only through detailed parsing of the frame can proper treatment be determined.

Parse results can (optionally) be passed to software.

### 5.10.5.1.2 FMan distribution and policing

After parsing is complete, there are two options for treatment, as shown in this table.

| Treatment                 | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Benefits                                                                                                                                                                                                                                           |

|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Hash                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Useful when spreading<br>traffic while obeying QoS<br>constraints is required                                                                                                                                                                      |

| Classification<br>look-up | <ul> <li>Looks up certain fields in the frame to determine subsequent action to take, including policing.</li> <li>The FMan contains internal memory that holds small tables for this purpose.</li> <li>The user configures the sets of lookups to perform, and the parse results dictate which one of those sets to use.</li> <li>Lookups can be chained together such that a successful look-up can provide key information for a subsequent look-up. After all the look-ups are complete, the final classification result provides either a hash key to use for spreading, or a FQ ID directly.</li> </ul> | <ul> <li>Useful when hash<br/>distribution is<br/>insufficient and a<br/>more detailed<br/>examination of the<br/>frame is required</li> <li>Can determine<br/>whether policing is<br/>required and the<br/>policing context to<br/>use</li> </ul> |

### Table 7. Post-parsing treatment options

Key benefits of the FMan policing function are as follows:

- Because the FMan has up to 256 policing profiles, any frame queue or group of frame queues can be policed to either drop or mark packets if the flow exceeds a preconfigured rate.

- Policing and classification can be used in conjunction to mitigate Distributed Denial of Service Attack (DDOS).

- The policing is based on the two-rate-three-color marking algorithm (RFC2698). The sustained and peak rates, as well as the burst sizes, are user-configurable. Therefore, the policing function can rate-limit traffic to conform to the rate that the flow is mapped to at flow set-up time. By prioritizing and policing traffic prior to software processing, CPU cycles can focus on important and urgent traffic ahead of other traffic.

Each FMan also supports PCD on traffic arriving from within the chip. This is referred to as off-line parsing, and it is useful for reclassification following decapsulation of encrypted or compressed packets.

FMan PCD supports virtualization and strong partitioning by delaying buffer pool selection until after classification. In addition to determining the FQ ID for the classified packet, the FMan also determines the 'storage profile.' Configuration of storage profiles (up to 32 per physical port) allows the FMan to store received packets using buffer pools owned by a single software partition, and enqueue the associated Frame Descriptor to a frame queue serviced by only that software partition.

#### Crip features

This capability includes copying from one buffer pool to another if the traffic is received via the FMan's off-line parsing port. Packets can be copied to multiple buffer pools and enqueued to multiple frame queues to support broadcast and multicast requirements.

### 5.10.5.2 Queue Manager

The Queue Manager (QMan) is the primary infrastructure component in the DPAA, allowing for simplified sharing of network interfaces and hardware accelerators by multiple CPU cores. It also provides a simple and consistent message and data passing mechanism for dividing processing tasks amongst multiple vCPUs.

The Queue Manager offers the following features:

- Common interface between software and all hardware

- Controls the prioritized queuing of data between multiple processor cores, network interfaces, and hardware accelerators.

- Supports both dedicated and pool channels, allowing both push and pull models of multicore load spreading.

- · Atomic access to common queues without software locking overhead

- Mechanisms to guarantee order preservation with atomicity and order restoration following parallel processing on multiple CPUs

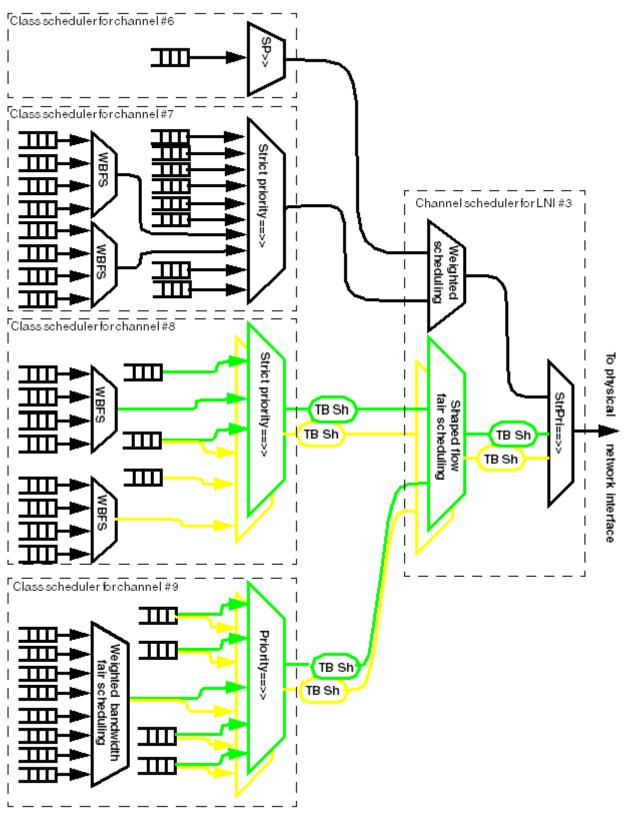

- Egress queuing for Ethernet interfaces

- Hierarchical (2-level) scheduling and dual-rate shaping

- Dual-rate shaping to meet service-level agreements (SLAs) parameters (1 Kbps...10 Gbps range, 1 Kbps granularity across the entire range)

- Configurable combinations of strict priority and fair scheduling (weighted queuing) between the queues

- Algorithms for shaping and fair scheduling are based on bytes

- Queuing to cores and accelerators

- Two level queuing hierarchy with one or more Channels per Endpoint, eight work queues per Channel, and numerous frame queues per work queue

- Priority and work conserving fair scheduling between the work queues and the frame queues

- · Loss-less flow control for ingress network interfaces

- Congestion avoidance (RED/WRED) and congestion management with tail discard

### 5.10.5.3 Buffer Manager

The Buffer Manager (BMan) manages pools of buffers on behalf of software for both hardware (accelerators and network interfaces) and software use.

The Buffer Manager offers the following features:

- Common interface for software and hardware

- Guarantees atomic access to shared buffer pools

- Supports 64 buffer pools

- Software, hardware buffer consumers can request different size buffers and buffers in different memory partitions

- Supports depletion thresholds with congestion notifications

- On-chip per pool buffer stockpile to minimize access to memory for buffer pool management

- LIFO (last in first out) buffer allocation policy

- Optimizes cache usage and allocation

- A released buffer is immediately used for receiving new data

### 5.10.5.4 SEC 5.0

The SEC 5.0 is Freescale's fifth generation crypto-acceleration engine. The SEC 5.0 is backward-compatible with the SEC 4.x, as implemented in the first generation of high-end QorIQ products, which includes the P4080. As in the SEC 4.x, the SEC 5.0 offers high performance symmetric and asymmetric encryption, keyed and unkeyed hashing algorithms, NIST-compliant random number generation, and security protocol header and trailer processing.

The SEC 5.0 can perform full protocol processing for the following security protocols:

- IPsec

- SSL/TLS

- 3GPP RLC encryption/decryption

- LTE PDCP

- SRTP

- IEEE 802.1AE MACSec

- IEEE 802.16e WiMax MAC layer

The SEC 5.0 supports the following algorithms, modes, and key lengths as raw modes, or in combination with the security protocol processing described above.

- Public Key Hardware Accelerators (PKHA)

- RSA and Diffie-Hellman (to 4096b)

- Elliptic curve cryptography (1023b)

- Data Encryption Standard Accelerators (DESA)

- DES, 3DES (2-key, 3-key)

- ECB, CBC, OFB, and CFB modes

- Advanced Encryption Standard Accelerators (AESA)

- Key lengths of 128-bit, 192-bit, and 256-bit

- ECB, CBC, CTR, CCM, GCM, CMAC, OFB, CFB, xcbc-mac, and XTS

- ARC Four Hardware Accelerators (AFHA)

- Compatible with RC4 algorithm

- Message Digest Hardware Accelerators (MDHA)

- SHA-1, SHA-256, 384, 512-bit digests

- MD5 128-bit digest

- HMAC with all algorithms

- Kasumi/F8 Hardware Accelerators (KFHA)

- F8, F9 as required for 3GPP

- A5/3 for GSM and EDGE, GEA-3 for GPRS

- Snow 3G Hardware Accelerators (SNOWf8 and SNOWf9)

- Implements Snow 3.0, F8 and F9 modes

- ZUC Hardware Accelerators (ZUCE and ZUCA)

- Implements 128-EEA3 & 128-EIA3

- CRC Unit

- Standard and user-defined polynomials

- Random Number Generator

- Incorporates TRNG entropy generator for seeding and deterministic engine (SHA-256)

- Supports random IV generation

The SEC 5.0 is designed to support bulk encryption at up to 40 Gbps, large packet/record IPsec/SSL at up to 30 Gbps, and 20 Gbps for IPsec ESP at Imix packet sizes. 3G and LTE algorithms are supported at 10 Gbps or more.

The SEC dequeues data from its QMan hardware portal and, based on FQ configuration, also dequeues associated instructions and operands in the Shared Descriptor. The SEC processes the data then enqueues it to the configured output FQ. The SEC uses the Status/CMD word in the output Frame Descriptor to inform the next consumer of any errors encountered during processing (for example, received packet outside the anti-replay window.)

### Figure 12. SEC 5.0 block diagram

The SEC 5.0 is also part of the QorIQ Platform's Trust Architecture, which gives the SoC the ability to perform secure boot, runtime code integrity protection, and session key protection. The Trust Architecture is described in Resource partitioning and QorIQ Trust Architecture.

## 5.10.5.5 Pattern Matching Engine (PME 2.1)

The PME 2.1 is Freescale's second generation of extended NFA style pattern matching engine. Unchanged from the first generation QorIQ products, it supports ~10 Gbps data scanning.

Key benefits of a NFA pattern matching engine:

- No pattern "explosion" to support "wildcarding" or case-insensitivity

- Comparative compilations have shown 300,000 DFA pattern equivalents can be achieved with ~8000 extended NFA patterns

- Pattern density much higher than DFA engines.

- Patterns can be stored in on-chip tables and main DDR memory

- Most work performed solely with on-chip tables (external memory access required only to confirm a match)

- No need for specialty memories; for example, QDR SRAM, RLDRAM, and so on.

- Fast compilation of pattern database, with fast incremental additions

- Pattern database can be updated without halting processing

- · Only affected pattern records are downloaded

- DFA style engines can require minutes to hours to recompile and compress database

Freescale's basic NFA capabilities for byte pattern scanning are as follows:

- The PME's regex compiler accepts search patterns using syntax similar to that in software-based regex engines, such as Perl-Compatible Regular Expression (PCRE).

- Supports Perl meta-characters including wildcards, repeats, ranges, anchors, and so on.

- Byte patterns are simple matches, such as gabcd123h, existing in both the data being scanned and in the pattern specification database.

- Up to 32 KB patterns of length 1-128 bytes

Freescale's extensions to NFA style pattern matching are principally related to event pattern scanning. Event patterns are sequences of byte patterns linked by 'stateful rules.' Freescale uses event pattern scanning and stateful rule processing synonymously. Stateful rules are hardware instructions by which users define reactions to pattern match events, such as state changes, assignments, bitwise operations, addition, subtraction, and comparisons.

Some key characteristics and benefits of the Stateful Rule extensions include:

- Ability to match patterns across data "work units" or packet boundaries

- Can be used to correlate patterns, qualify matches (for example, contextual match), or to track protocol state change

- Easily support "greedy" wildcards

- For example, ABC.\*DEF == two patterns tied together by a stateful rule

- Delays the need for software post-processing. Software is alerted after all byte patterns are detected in the proper sequence, rather than any time a byte pattern is detected.

- Implements a significant subset of the regex pattern definition syntax as well as many constructs which cannot be expressed in standard PCRE

- PME 2.1 supports up to 32K stateful rules, linking multiple byte patterns

The PME 2.1 dequeues data from its QMan hardware portal and, based on FQ configuration, scans the data against one of 256 pattern sets, 16 subsets per pattern set.

When the PME finds a byte pattern match, or a final pattern in a stateful rule, it generates a report.

### 5.10.5.6 Decompression and Compression Engine (DCE 1.0)

The Decompression and Compression Engine (DCE 1.0) is an accelerator compatible with Datapath Architecture providing lossless data decompression and compression for the QorIQ family of SoCs. The DCE supports the raw DEFLATE algorithm (RFC1951), GZIP format (RFC1952) and ZLIB format (RFC1950). The DCE also supports Base 64 encoding and decoding (RFC4648).

The DEFLATE algorithm is a basic building block for data compression in most modern communication systems. It is used by HTTP to compress web pages, by SSL to compress records, by gzip to compress files and email attachments, and by many other applications.

Deflate involves searching for repeated patterns previously seen in a Frame, computing the length and the distance of the pattern with respect to the current location in the Frame, and encoding the resulting information into a bitstream.

The decompression algorithm involves decoding the bitstream and replaying past data. The Decompression and Compression Engine is architected to minimize the system memory bandwidth required to do decompression and compression of Frames while providing multi-gigabits per second of performance.

Detailed features include the following:

- Deflate; as specified as in RFC1951

- GZIP; as specified in RFC1952

- Zlib; as specified in RFC1950

- Interoperable with the zlib 1.2.5 compression library

- Compression

- ZLIB, GZIP and DEFLATE header insertion

- ZLIB and GZIP CRC computation and insertion

- Zlib sync flush and partial flush for chunked compression (for example, for HTTP1.1)

- Four modes of compression

- No compression (just add DEFLATE header)

- Encode only using static/dynamic Huffman codes

- Compress and encode using static Huffman codes

- Compress and encode using dynamic Huffman codes

- Uses a 4KB sliding history window

- Supports Base 64 encoding (RFC4648) after compression

- Provides at least 2.5:1 compression ratio on the Calgary Corpus

- Decompression supports:

- ZLIB, GZIP and DEFLATE header removal

- ZLIB and GZIP CRC validation

- 32KB history

- Zlib flush for chunked decompression (for HTTP1.1 for example)

- Jup features

- · All standard modes of decompression

- No compression

- Static Huffman codes

- Dynamic Huffman codes

- Provides option to return original compressed Frame along with the uncompressed Frame or release the buffers to BMan

- Does not support use of ZLIB preset dictionaries (FDICT flag = 1 is treated as an error).

- Base 64 decoding (RFC4648) prior to decompression

The DCE 1.0 is designed to support up to 8.8 Gbps for either compression or decompression, or 17.5 Gbps aggregate at ~4 KB data sizes.

### 5.10.6 DPAA capabilities

Some DPAA features and capabilities have been described in the sections covering individual DPAA components. This section describes some capabilities enabled by DPAA components working together.

### 5.10.6.1 Ingress policing and congestion management

In addition to selecting FQ ID and storage profile, classification can determine whether policing is required for a received packet, along with the specific policing context to be used.

FMan policing capabilities include the following:

- RFC2698: two-rate, three-color marking algorithm

- RFC4115: Differentiated service two-rate, three-color marker with efficient handling of in-profile traffic

- Up to 256 internal profiles

The sustained and peak rates, and burst size for each policing profile are user-configurable.

### 5.10.6.2 Customer-edge egress-traffic management (CEETM)

Customer-edge egress-traffic management (CEETM) is a DPAA enhancement first appearing in the T4240. T4240 continues to support the work queue and frame queue scheduling functionality available in the P4080 and other first generation QorIQ chips, but introduces alternative functionary, CEETM, that can be mode selected on a network interface basis to support the shaping and scheduling requirements of carrier Ethernet connected systems.

### 5.10.6.2.1 CEETM features

Each instance of CEETM (one per FMan) provides the following features:

- Supports hierarchical multi-level scheduling and shaping, which:

- is performed in an atomic manner; all context at all levels is examined and updated synchronously.

- employs no intermediate buffering between class queues and the direct connect portal to the FMan.

- Supports dual-rate shaping (paired committed rate (CR) shaper and excess rate (ER) shaper) at all shaping points.

- Shapers are token bucket based with configurable rate and burst limit.

- Paired CR/ER shapers may be configured as independent or coupled on a per pair basis; coupled means that credits to the CR shaper in excess of its token bucket limit is credited to the ER bucket

- Supports eight logical network interfaces (LNI)

- Each LNI:

- aggregates frames from one or more channels.

- priority schedules unshaped frames (aggregated from unshaped channels), CR frames, and ER frames (aggregated from shaped channels)

- applies a dual-rate shaper to the aggregate of CR/ER frames from shaped channels

- can be configured (or reconfigured for lossless interface failover) to deliver frames to any network interface.

- Supports 32 channels available for allocation across the eight LNIs

- Each channel:

- can be configured to deliver frames to any LNI.

- can be configure to be unshaped or shaped; when shaped, a dual rate shaper applies to the aggregate of CR/ER frames from the channel.

- has eight independent classes and eight grouped classes; grouped classes can be configured as one class group of eight or as two class groups of four.

- supports weighted bandwidth fairness within grouped class groups with weights configured on a channel and class basis.

- strict priority scheduling of the eight independent classes and the aggregate(s) of the grouped classe(s); the priority of each of the two class groups can be independently configured to be immediately below any of the independent classes.

- is configurable such that each of the eight independent classes and two class groups can supply CR frames, ER frames or both when channel is configured to be shaped.

- is configured independently.

- Each class:

- has a dedicated class queue (CQ) with equivalent congestion management functionality available to FQs.

- can have a dedicated or shared Congestion Management Record supports sufficient number of CMRs for all CQs to have a dedicated CMR, if desired.