Uutiset

DAC tutkii AI: n ja ML: n roolia eri markkinoilla

Moscone Center, San Francisco, isännöi DAC: n 25.-28.6

OneSpin-ratkaisut ja Austemper Design Systems korostavat työkaluja toiminnallisen turvallisuuden varmistamiseen. Austemper keskittyy kriittisten järjestelmien kehittämiseen KaleidoScope-työkalupaketilla, joka tukee analogista suunnittelua samanaikaisen, sekasignaalin vian etenemiselle. Automaattisella työkalupaketilla on turvallisuusanalyysi, synteesi ja todentamisominaisuudet sertifiointiin suuntautuville sovelluksille. Sitä käytetään laajamittaiseen autoteollisuuteen ADAS-järjestelmässä ja itsenäisessä ajossa. Samanaikaisen vian simulointiin sisältyy ISO 26262: n suosittelemia simulaatioita ASIL-vaatimusten noudattamiseksi.

Yhtiö solmi äskettäin yhdessä OneSpin Solutionsin kanssa työkalupohjaisen toimintatapojen käyttöönottamisen menetelmän, joka yhdistää suunnittelu- ja verifikaatiovirtauksen, joka ilmenee OneSpin-kabinetissa. Laitteiden turvallisuusmekanismeja lisätään siruihin ja OneSpin Solutionsin työkalut vahvistavat muodollisesti laitteisturvallisuuslogiikan. Vastaavuusvaatimukset varmistavat, että lisätty turvallisuuslogiikka ei vaikuta säännöllisiin toimintoihin ja virheentunnistusanalyysi varmistaa, että turvamekanismit toimivat kunnolla satunnaisten virheiden tapahtuessa.

OneSpin edistä myös Tool Qualification -sarjaaan sen jälkeen, kun TÜV SÜD on tarkistanut sen työkalujen kehittämisprosessit. Alkuperäinen sarja on saatavana yhtiön 360 EC-FPGA EDA -työkaluille, automaattiselle sekvenssien vastaavuustarkistukselle, joka estää FPGA-suunnitteluvirtauksia toteutusvirheiden käyttöönotosta. Pakkaus on sertifioitu ISO 26262, IEC 61508 ja EN 50128 mukaan.

FPGA-näkemyksiä

Still FPGA-suunnittelussa, Plunify on tehnyt yhteistyötä Xilinxin kanssa tarjotakseen Vivadon design-sarjan pilvessä Plunify Cloud -alustan kautta. Suunnittelijat maksavat jopa 50c: n verran Vivado-hankkeen kääntämistä Amazon Web Services (AWS) -pilvalle, mukaan lukien lisenssit.

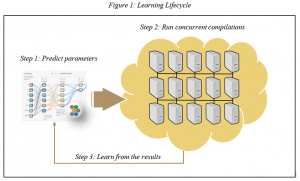

Yhtiö myös osoittaa parannuksia InTime-ajastuksen sulkemisohjelmistoihinsa FPGA-ajastuksen optimoimiseksi pilvessä (kuva 1). InTime-optimointimenetelmä voi parantaa kellotaajuutta 20 - 80% ja täyttää ajoitusvaatimukset päivinä eikä viikoina koneen oppimisen kautta. Ohjelmisto myös kiihdyttää ajoituksen sulkemista ja optimointia ja sitä käytetään pilven kautta.

Yhtiö myös osoittaa parannuksia InTime-ajastuksen sulkemisohjelmistoihinsa FPGA-ajastuksen optimoimiseksi pilvessä (kuva 1). InTime-optimointimenetelmä voi parantaa kellotaajuutta 20 - 80% ja täyttää ajoitusvaatimukset päivinä eikä viikoina koneen oppimisen kautta. Ohjelmisto myös kiihdyttää ajoituksen sulkemista ja optimointia ja sitä käytetään pilven kautta.

EFPGA-tekniikan, Achronix Semiconductor tekee yhteistyötä IP-asiantuntijan kanssa HEITTÄÄ lisätä tulostusnopeutta ja säästää muistia.

Kaksi näytteilleasettajaa selittää, miten CASTin häviötön pakkaus IP on siirretty Achronix FPGA -portaaliin datakeskukseen ja mobiilireunan tiedonsiirtosovelluksiin. Häviämättömän pakkaustason standardi Deflate, GZIP ja ZLIB on yhteensopiva puristukseen tai dekompressioon käytettävien ohjelmistoteutusten kanssa, jotta voidaan tarjota jopa 100 Gbit / s: n läpäisykyky alhaisella puristuksella ja alhaisella viiveellä yhdistettynä Speedcore eFPGA -tekniikkaan suurien tietoja alhaisella virrankulutuksella.

CAST on siirtänyt IP-osoitteensa Achronixin FPGA: eille

Energiatehokkuus

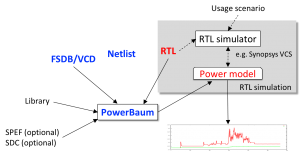

Puhuminen virranhallinnasta, toinen näytteilleasettaja, Baum, tunnistaa energiatehokkuuden alimpana kehittyneenä alueena sirujen suunnittelussa. Sen automaattinen tehoanalyysi ja mallinnustyökalu on suunniteltu autoteollisuudelle, IoT: lle, mobiililaitteille, verkko- ja palvelinprojekteille. PowerBaum 2.0 (kuvio 3) tukee dynaamista ja staattista tehoa ottaen RTL- ja netlist-kuvaukset ja lisää tukea tehoanalyysin avulla laitteiston emuloinnilla. Tämä, sanoo yritys, antaa insinööreille mahdollisuuden korjata tehohäviöt realistisissa ohjelmistokenaarioissa. Työkalu tukee myös analyysia, jonka suunnittelijat ovat määritelleet mielivaltaisilla lämpötiloilla, mitkä ovat lämpötilan vaikutukset suunnittelun tehonkulutukseen.

DAC: ssa yhtiö esittelee PowerWurzelin, PowerBaumin integroitavan portitason tehoanalyysimoottorin tehomallinnukseen.

Kuva 3 Baumin työkalut analysoivat energiatehokkuutta

Cloud-pohjainen SoC-suunnittelu ja vahvistusvälineet IC-suunnittelulle metrics sisältää Cloud Simulator ja Verification Manager, joka on suunniteltu hallitsemaan simulointivaatimuksia ja resursseja ja säätämään niitä joka minuutti. Yhtiö väittää, että Google Cloud mahdollistaa rajoittamattoman UVM-yhteensopivan SystemVerilog-simulointikapasiteetin ja natiivin, web-pohjaisen vahvistuksen hallinnan nopeampien regressioaikojen, tavallisten koodien virheiden ja ennustettavan koodin kattavuuden vähentämiseksi.

Näytteilleasettajien lisäksi tapahtuma järjestää teknisiä istuntoja ja ajankohtaisia alueita käsittelevän keynotes-ohjelman. Esimerkiksi Cadence järjestää tänä vuonna tutoriaalin "Automaattinen turvallisuus ja luotettavuus autoteollisuuden sovelluksiin" ja toinen koneoppimisesta ("Machine Learning ottaa puheentunnistuksen suorituskykyä seuraavalle tasolle"). Instrumentaalinen, Anna-Katrina Shedletsky, keisarikirja, keskiviikko 25. kesäkuuta, keskittyy "Automaation älykkyyden: koneen oppiminen ja valmistus tulevaisuuden". Maami Matarić, Etelä-Kalifornian yliopisto, esittelee "Automation vs. Augmentation: Socially Assistive Robotocs ja Future of Work" -tutkimuksen torstaina esittämällä ML: n ja AI: n sosiaalisesti avustavaa robotiikkaa (SAR).

Toinen keynote kannattaakin RISC-V: tä keinona vapaalle arkkitehdille omistetuista opetusjoukkoarkkitehtuureista (ISA). David A Patterson, Google ja Kalifornian yliopisto esittelevät uuden arkkitehtuurin arkkitehtuuria: domain-specific accelerators ja Open RISC-V.

Tänä vuonna DAC: n uusi alue on Design Infrastructure Alley. Puheenjohtaja ESD Alliance ja yhdistys korkean suorituskyvyn tietotekniikan ammattilaisille on alue, joka on omistettu IT-infrastruktuurille sähköisten järjestelmien ja komponenttien suunnittelussa. Pilottien suunnittelun ja hallinnan tietotekniikka- ja tallennusvaatimukset ovat lisäksi oma Design-on-the-Cloud-paviljongin teatteri, jossa käsitellään lisenssihallintaa, grid-tietojenkäsittelyä ja tietoturvaa.